## **UNIVERSIDADE FEDERAL DO PAMPA**

**Anderson de Paula Fortes**

# PROJETO AUTOMÁTICO DE CIRCUITOS INTEGRADOS ANALÓGICOS UTILIZANDO METAHEURÍSTICAS BIO-INSPIRADAS

Alegrete 24/08/2018

#### **Anderson de Paula Fortes**

# PROJETO AUTOMÁTICO DE CIRCUITOS INTEGRADOS ANALÓGICOS UTILIZANDO METAHEURÍSTICAS BIO-INSPIRADAS

Dissertação apresentada ao Programa de Pós-graduação Stricto Sensu em Engenharia Elétrica da Universidade Federal do Pampa, como requisito parcial para obtenção do Título de Mestre em Engenharia Elétrica.

Orientador: Alessandro Girardi

Alegrete 24/08/2018

# Ficha catalográfica elaborada automaticamente com os dados fornecidos pelo(a) autor(a) através do Módulo de Biblioteca do Sistema GURI (Gestão Unificada de Recursos Institucionais).

F738p Fortes, Anderson de Paula

Projeto automático de circuitos integrados analógicos utilizando metaheurísticas bio-inspiradas / Anderson de Paula Fortes.

99 p.

Dissertação(Mestrado) -- Universidade Federal do Pampa, MESTRADO EM ENGENHARIA ELÉTRICA, 2018.

"Orientação: Alessandro Gonçalves Girardi".

1. Circuitos Analógicos. 2. Otimização. 3. Amplificadores. 4. OTA Miller. 5. Telescopic. I. Título.

#### Anderson de Paula Fortes

# PROJETO AUTOMÁTICO DE CIRCUITOS INTEGRADOS ANALÓGICOS UTILIZANDO METAHEURÍSTICAS BIO-INSPIRADAS

Dissertação apresentada ao Programa de Pós-graduação Stricto Sensu em Engenharia Elétrica da Universidade Federal do Pampa, como requisito parcial para obtenção do Título de Mestre em Engenharia Elétrica.

Área de concentração: Sistemas de Energia

Dissertação defendida e aprovada em: Alegrete, 24 de Agosto de 2018. Banca examinadora:

Alessandro Girardi

Orientador

Cesar Ramos Rodrigues

**UFSM**

Jumar Russi

Unipampa

Marcelo CaggianiLuizelli

Unipampa

#### **AGRADECIMENTOS**

Agradeço a Deus por me privilegiar, me abençoar com todas as coisas necessárias para que eu possa ir atrás dos meus objetivos e por estar comigo, tanto nas horas boas quanto nas mais difíceis.

Aos meus pais, Francisco e Iara, por sempre fazerem tudo que estivesse ao alcance, abrindo mão de muitas coisas para que eu e minhas irmãs pudéssemos estudar. Pelos bons exemplos de luta e por me incentivarem a me tornar alguém digno.

Às minhas irmãs, Margiani, Luciani e Carolini, pela amizade e companheirismo durante a vida toda.

Aos meus mestres, professores do ensino fundamental à pós-graduação, pelo ensinamento que me deram, presente mais valioso e que nunca alguém poderá me tirar. Em especial à memória da prof. Márcia Cera, exemplo de grande profissional, amiga e fonte de inspiração como docente.

Ao meu orientador, prof. Alessandro Girardi, pela oportunidade dada a mim de realizar este trabalho ao seu lado. Agradeço pela paciência, por sempre ajudar, incentivar, mostrar o caminho correto a ser seguido durante o desenvolvimento deste trabalho e pelo exemplo de grande profissional.

Aos meus colegas e amigos do grupo GAMA e demais amigos que fiz na universidade pelas parcerias nas madrugadas de estudo, ajudas nos trabalhos, churrascos e cervejas. Levarei a amizade de vocês para a vida toda. Agradeço de coração a todas as pessoas que trabalham na universidade, por nos darem segurança, ambiente limpo e agradável, sem os quais o ensino não seria possível.

O presente trabalho foi realizado com apoio da Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Código de Financiamento 001, portanto, deixo aqui meus agradecimentos também à CAPES.

"Vinde a mim todos que estais cansados e sobrecarregados,

e eu vos aliviarei.

Tomai sobre vós o meu jugo

e aprendei de mim,

porque sou manso e humilde de coração;

e achareis descanso para vossa alma.

Porque o meu jugo é suave,

E meu fardo é leve ."

(Jesus de Nazaré)

#### **RESUMO**

A contínua redução das dimensões e tensões de alimentação dos circuitos integrados torna os processos de otimização e fabricação dos circuitos mais complexos. A parte analógica de um circuito integrado misto representa uma grande parcela no esforço de dimensionamento do circuito. É necessário dimensionar cada dispositivo do circuito separadamente de forma a atingir as especificações desejadas para o circuito. Cada componente de um circuito analógico, seja ele um transistor, resistor ou capacitor, representa uma ou mais variáveis, como, por exemplo, o comprimento e largura do canal de um transistor. Em circuitos com muitas variáveis, a combinação de dimensões dos diferentes componentes é muito grande, o que torna o processo de dimensionamento e ajuste dos valores muito complexo. O projetista precisa dimensionar cada um dos componentes e verificar se o circuito atende ao desempenho desejado. Esse processo de dimensionamento de circuito integrado analógico pode ser modelado como um problema de otimização e resolvido por heurísticas de otimização. No entanto, a capacidade das heurísticas para explorar o espaço de busca tem uma grande influência no resultado do dimensionamento do circuito. Neste trabalho, implementou-se duas metaheurísticas bio-inspiradas para dimensionar amplificadores operacionais em tecnologia CMOS: Cuckoo Search (CS) e Firefly. Os resultados são comparados com o dimensionamento utilizando a heurística Particle Swarm Optimization (PSO). Ademais, realizou-se um estudo acerca do critério de parada para os algoritmos propostos e também sobre os valores iniciais para as variáveis livres. Os resultados mostram que PSO e CS são mais adequados para alcançar o desempenho requerido que atenda às especificações do circuito, enquanto o FA apresenta dificuldade em pesquisar eficientemente o espaço de projeto. Além disso, os resultados mostram que heurísticas são apropriadas para o dimensionamento automático de circuitos analógicos e podem levar a resultados melhores do que no processo manual.

**Palavras-chave**: Circuitos Analógicos, Otimização, Ota Miller, Telescopic, Amplificadores, Cuckoo Search, Firefly Algorithm, Particle Swarm Optimization.

#### **ABSTRACT**

The continuous reduction of the dimensions and supply voltages of the integrated circuits makes the optimization and manufacturing processes of the circuits more complex. The analog part of a mixed integrated circuit represents a large part of the circuit sizing effort. It is necessary to dimension each device of the circuit separately in order to reach the specifications desired for the circuit. Each component of an analog circuit, whether it is a transistor, resistor, capacitor or etc., represents one or more variables, such as the length and width of the channel of a transistor. In circuits with many variables, the combination of dimensions of the different components is very large, which makes the process of sizing and adjusting the values very complex. The designer needs to scale each of the components and check if the circuit meets the desired performance aspects. This analog integrated circuit sizing process can be modeled as an optimization problem and solved by optimization heuristics. However, the ability of heuristics to explore the search space has a great influence on the result of the circuit sizing. In this work, two bio-inspired metaheuristics were implemented to size three operational amplifiers in CMOS technology: Cuckoo Search (CS) and Firefly and compared with the results of sizing with Particle Swarm Optimization (PSO). In addition, a study was carried out on the stopping criterion for the proposed algorithms and also on the initial values for the free variables. The results show that PSO and CS are more adequate to achieve the required performance that meets the specifications of the circuit, while the FA presents difficulty in efficiently searching the design space. In addition, the results show that heuristic algorithms are suitable for the automatic sizing of analog circuits and can lead to better results than in the manual process.

**Keywords**: Analog Circuits, Optimization, Miller OTA, Telescopic, Amplifiers, Cuckoo Search, Firefly Algorithm, Particle Swarm Optimization.

# LISTA DE ILUSTRAÇÕES

| Figura 1 – Níveis de projeto de um circuito analógico                                | 28 |

|--------------------------------------------------------------------------------------|----|

| Figura 2 – Estrutura física de um transistor em tecnologia CMOS                      | 29 |

| Figura 3 – Fluxo básico de um modelo baseado em otimização                           | 31 |

| Figura 4 – Fluxo de projeto da ferramenta UCAF                                       | 39 |

| Figura 5 – Fluxograma de execução do núcleo da ferramenta                            | 40 |

| Figura 6 – Esquemático de um OTA Miller em tecnologia CMOS                           | 41 |

| Figura 7 – Netlist representando o OTA Miller da figura 6                            | 42 |

| Figura 8 – Exemplo de arquivo de parâmetro gerado pela ferramenta UCAF               |    |

| para o circuito da figura 6                                                          | 43 |

| Figura 9 – Configuração de circuito para medição de características AC               | 44 |

| Figura 10 – Netlist gerado pela ferramenta representando o circuito da figura 9      | 45 |

| Figura 11 – Configuração de circuito para medição do slew rate                       | 45 |

| Figura 12 – Resposta de saída para medição de taxa de variação                       | 46 |

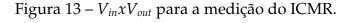

| Figura 13 – $V_{in}xV_{out}$ para a medição do ICMR                                  | 46 |

| Figura 14 – Configuração de circuito para medição do output swing                    | 47 |

| Figura 15 – Medição $V_{in}xV_{out}$ para extração do output swing                   | 47 |

| Figura 16 – Métricas de avaliação das restrições de projeto: (a) especificação de    |    |

| valor mínimo exigido e (b) especificação de valor máximo exigido                     | 50 |

| Figura 17 – Gráfico que mostra o impacto das especificações não atendidas na         |    |

| função custo e sua evolução                                                          | 51 |

| Figura 18 – Algumas das heurísticas propostas nas últimas décadas                    | 55 |

| Figura 19 – (a): Movimento browniano. (b): Vôo de Lévy                               | 58 |

| Figura 20 – Ilustração do funcionamento do processo de atratividade dos vagalu-      |    |

| mes                                                                                  | 61 |

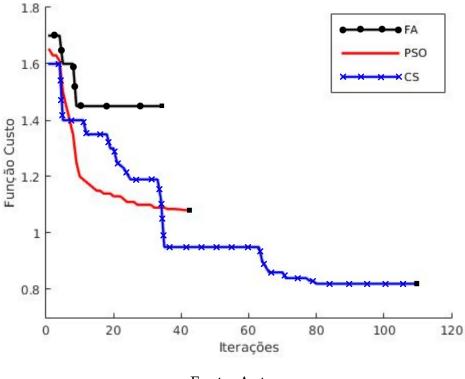

| Figura 21 – Evolução da função custo para o FA, PSO e CS utilizando h=30             | 68 |

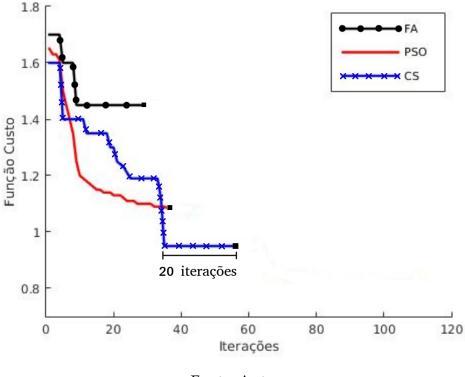

| Figura 22 – Representação da mesma execução da figura 21 mas com h=20                | 69 |

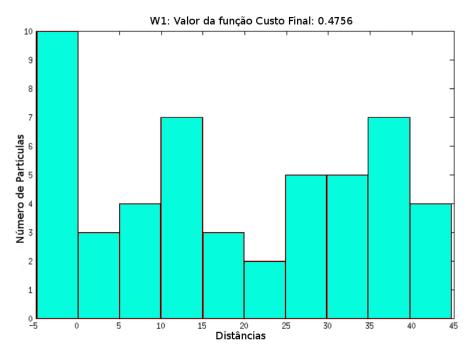

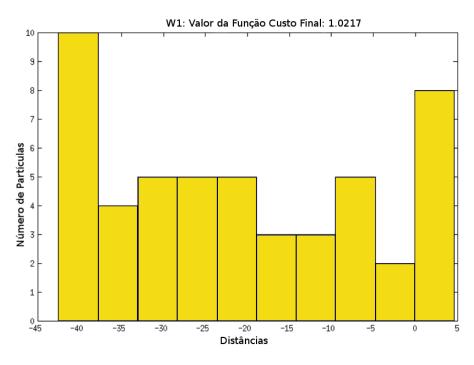

| Figura 23 – Distribuição das partículas iniciais para W1                             | 71 |

| Figura 24 – Distância das posições iniciais das partículas para o melhor valor final |    |

| de W1                                                                                | 72 |

| Figura 25 – Distância das posições iniciais das partículas para o pior valor final   |    |

| de W1                                                                                | 73 |

| Figura 26 – Esquemático de um OTA Miller em tecnologia CMOS                          | 75 |

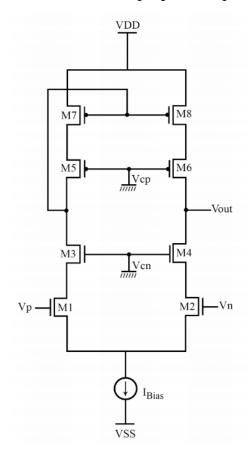

| Figura 27 – Esquemático do OTA de 0.25V proposto por Ferreira e Sonkusale (2014      | 84 |

| Figura 28 – Uma matriz retangular de transistores nMOS com implantes de halo         |    |

| (à esquerda) e seu transistor equivalente (à direita)                                | 85 |

| Figura 29 – Netlist representando o sub-circuito M1a                                 | 85 |

| Figura 30 – Netlist que faz a chamada dos sub-circuitos de transistores              | 86 |

| Figura 31 – Esquemático de um amp-op telescopic em tecnologia CMOS                   | 89 |

# **LISTA DE TABELAS**

| Tabela 1 — Trabalhos sobre otimização automática de CIs analógicos               | 33 |

|----------------------------------------------------------------------------------|----|

| Tabela 2 – Resultados para as 3 diferentes formas de inicialização das variáveis |    |

| livres                                                                           | 70 |

| Tabela 3 – Valor médio da função custo variando o número de ninhos               | 77 |

| Tabela 4 – Valor médio da função custo variando o parâmetro pa                   | 77 |

| Tabela 5 — Resultados variando $\alpha$                                          | 78 |

| Tabela 6 – Resultados variando $\beta$                                           | 79 |

| Tabela 7 – Valor médio da função custo variando o número de vagalumes            | 79 |

| Tabela 8 – Número de iterações e valor da função custo obtida                    | 80 |

| Tabela 9 – Especificações para os melhores resultados de cada algoritmo de       |    |

| otimização avaliado.                                                             | 80 |

| Tabela 10 – OTA Miller: Análise típica e análises de Corners                     | 82 |

| Tabela 11 – Indicadores de desempenho obtidos para o OTA Miller alimentado       |    |

| pelo substrato                                                                   | 87 |

| Tabela 12 – Valores das variáveis após a otimização                              | 88 |

| Tabela 13 – <i>Bulk-driven</i> OTA Miller: Análise típica e análises de Corners  | 88 |

| Tabela 14 – Especificações para os melhores resultados de cada algoritmo de      |    |

| otimização avaliado.                                                             | 90 |

| Tabela 15 – Valores das variáveis após a otimização                              | 90 |

| Tabela 16 – Telescopic: Análise típica e análises de Corners                     | 90 |

# SUMÁRIO

| 1     | INTRODUÇÃO                                                  | 21 |

|-------|-------------------------------------------------------------|----|

| 1.1   | Objetivo                                                    | 24 |

| 1.2   | Organização do Trabalho                                     | 25 |

| 2     | PROJETO DE CIRCUITOS ELETRÔNICOS ANALÓGICOS                 | 27 |

| 2.1   | Projeto Automático de ICs Analógicos                        | 29 |

| 2.2   | Trabalhos Relacionados                                      | 31 |

| 2.2.1 | Métodos baseados no conhecimento                            | 32 |

| 2.2.2 | Métodos baseados em otimização                              | 32 |

| 2.2.3 | Conclusão                                                   | 37 |

| 3     | A FERRAMENTA UCAF                                           | 39 |

| 3.1   | Núcleo Principal                                            | 40 |

| 3.2   | Especificações e Testbenches                                | 42 |

| 3.3   | Bloco de Otimização                                         | 47 |

| 3.4   | Função Custo                                                | 48 |

| 3.5   | Conclusão                                                   | 51 |

| 4     | HEURÍSTICAS DE OTIMIZAÇÃO                                   | 53 |

| 4.1   | Algoritmos Bio-Inspirados                                   | 54 |

| 4.2   | Cuckoo Search via vôos de Lévy                              | 56 |

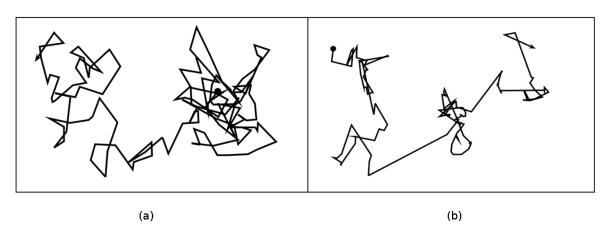

| 4.2.1 | Vôos de Lévy                                                | 56 |

| 4.2.2 | Funcionamento do Algoritmo Cucko Search                     | 58 |

| 4.3   | Algoritmo FireFly                                           | 60 |

| 4.3.1 | Atratividade                                                | 61 |

| 4.3.2 | Distância e movimento                                       | 62 |

| 4.4   | Particle Swarm Optimization                                 | 63 |

| 4.5   | Critério de Parada                                          | 65 |

| 4.6   | Estudo sobre os valores iniciais                            | 68 |

| 4.7   | Conclusão                                                   | 72 |

| 5     | RESULTADOS                                                  | 75 |

| 5.1   | Amplificador Operacional de Transcondutância do tipo Miller | 75 |

| 5.1.1 | Calibragem dos Parâmetros no CS                             | 76 |

| 5.1.2 | calibragem dos Parâmetros no FA                             | 78 |

| 5.1.3 | Comparação entre os algoritmos                              | 79 |

| 5.1.4 | Análise de Corners                                          | 81 |

| 5.2   | OTA Miller de Baixa Tensão Alimentado pelo Substrato        | 83 |

| 5.3   | Amplificador Operacional Telescopic                         | 87 |

| 5.4 | Conclusão   | 89 |

|-----|-------------|----|

| 6   | CONCLUSÃO   | 91 |

|     | REFERÊNCIAS | 93 |

# 1 INTRODUÇÃO

A demanda por sistemas integrados de baixo custo, baixa potência e baixa tensão tem aumentado em todas áreas de engenharia. Além disso, existe uma constante redução na dimensão dos componentes elétricos enquanto busca-se melhorar seus desempenhos.

O desenvolvimento da microeletrônica nas ultimas décadas possibilitou que circuitos eletrônicos sejam cada vez mais integrados. Esses circuitos, atualmente, são construídos em escalas micrométricas ou nanométricas sobre elementos semicondutores como o silício.

A contínua redução das dimensões e tensões de alimentação dos circuitos integrados (CI) torna a otimização e fabricação dos circuitos mais complexos, lentos e mais dependentes dos processos de fabricação e variações ambientais, tais como temperatura, radiação, etc (MORETO et al., 2012). Além disso, existe também uma forte tendência em desenvolver equipamentos em um único chip que reúna tanto os circuitos digitais quanto os analógicos. Isto tem gerado uma grande necessidade de projetistas desses CIs.

Embora a maioria das funções dos sistemas integrados sejam implementadas para o processamento de sinais digitais, os circuitos analógicos são essenciais em muitas aplicações. Existem algumas funções que necessariamente serão analógicas, como por exemplo a entrada de um circuito proveniente de um sensor, microfone, antena, rede, entre outros. Esses sinais devem ser recebidos ou detectados e, em seguida, amplificados e filtrados até um nível que permita a digitalização desse sinal.

A parte analógica, mesmo representando uma pequena fração de um circuito eletrônico (cerca de 20%), é a parte mais difícil de projetar devido à natureza complexa e a alta necessidade de conhecimento de circuitos analógicos por parte do projetista (VURAL, 2012). Esta área, mesmo sendo pequena, representa cerca de 40% de todo o esforço de projeto. Isso se deve ao fato de que o projeto geralmente é realizado de forma manual, sem o uso de ferramentas de automação.

Atualmente existem diversas ferramentas de projeto assistidas por computador (CAD) para auxiliar o fluxo de projeto dos CIs digitais. Por outro lado, poucas ferramentas CAD profissionais são dedicadas a auxiliar no projeto de CIs analógicos, como as ferramentas proprietárias fornecidas pelas empresas CADENCE®, Synopsys® ou Mentor Graphics®.

No dimensionamento dos transistores, por exemplo, os circuitos analógicos são mais complexos se comparados aos circuitos digitais. Nos circuitos digitais todos os transistores possuem tamanhos pré-definidos, ao contrário dos analógicos, em que cada transistor deve ser dimensionado individualmente (SEVERO, 2012).

O projeto de um CI analógico fundamentalmente depende do conhecimento e da experiência do projetista, visto que eles são sistemas que possuem muitas variáveis livres, isto é, possuem muitos parâmetros que podem ser modificados, como dimensões de cada componente do CI (comprimento e largura do gate dos transistores, resistores, capacitores e etc).

Em um circuito analógico simples, com 6 transistores, por exemplo, um capacitor e uma fonte de corrente, existem variáveis representando o comprimento e largura do gate dos 6 transistores, uma representando a capacitância e uma que define a corrente, totalizando 14 variáveis livres. Existe uma grande combinação de valores para as variáveis livres que devem ser investigadas a fim de atender às especificações de projeto. Os projetistas precisam atribuir um valor a cada variável, ou seja, dimensionar cada componente integrado, sejam eles transistores, resistores, capacitores e até mesmo indutores (BARROS; GUILHERME; HORTA, 2007; ALPAYDIN; BALKIR; DUNDAR, 2003; GIELEN; RUTENBAR, 2000). Alguns exemplos de especificações de projeto são o ganho de tensão, a margem de fase, o consumo de potência, a velocidade de resposta, área do gate, entre outros.

O projeto de CIs analógicos é geralmente constituído de três principais passos. Primeiro é definida uma dentre as várias arquiteturas e topologias possíveis para o circuito. O segundo passo é determinar os valores de parâmetros do circuito (resistência e valores de capacitores, geometrias de dispositivos, tais como comprimento e largura de transistores MOS) (JAFARI et al., 2010; TAHERZADEH-SANI et al., 2003). O terceiro passo consiste no desenho do leiaute representando o CI fisicamente.

O processo de dimensionamento pode ser realizado através de duas abordagens diferentes: baseado no conhecimento ou baseado em otimização. A idéia básica do projeto baseado no conhecimento é formular equações de projeto de tal forma que, dadas as características de desempenho desejadas para o CI, os parâmetros de projeto possam ser calculados.

Na síntese baseada no conhecimento utiliza-se uma metodologia de projeto que geralmente emprega equações de primeira ordem, com o objetivo de definir inicialmente as dimensões dos transistores e atender a alguns poucos objetivos de projeto, tais como o ganho de tensão e a frequência de ganho de tensão unitário (GIELEN; RUTENBAR, 2000). A partir disso, o projetista faz uso de simuladores do tipo SPICE (*Simulated Program with Integrated Circuits Emphasis*) para fazer pequenos ajustes nas dimensões e parâmetros dos transistores a fim de alcançar as especificações do projeto.

Esse procedimento de ajuste dos parâmetros é realizado geralmente através da mudança de um único parâmetro ou mesmo apenas uma das dimensões de um dos transistores e, a partir disso, o projetista avalia os novos resultados obtidos verificando se um determinado objetivo de projeto foi alcançado e também não foram degradados os demais objetivos (MORETO et al., 2012). Esse processo interativo e repetitivo entre o projetista e o simulador é muito trabalhoso, lento e por isso é totalmente dependente da experiência do projetista. Outras desvantagens são o grande tempo de preparo

necessário para desenvolver equações, a dificuldade de usá-las em uma tecnologia diferente e a limitação a um conjunto de circuitos.

Muitos circuitos a serem dimensionados apresentam um grande número de variáveis livres a serem determinadas. Nesses casos, métodos baseados em equações de primeira ordem e processo manual interativo usando o simulador SPICE e busca aleatória, por exemplo, geralmente são ineficientes quando muitas especificações de projeto são consideradas, devido ao espaço de busca ser extremamente grande. Em um circuito com 24 variáveis livres, por exemplo, o número de combinações possíveis no espaço de projeto pode ultrapassar a ordem de  $10^{40}$ , o que é muito grande para avaliar com uma técnica exaustiva. Nesse caso, o tempo e o custo do projeto do circuito se tornam altos, além de ser bastante difícil se atender a todas as especificações desejadas.

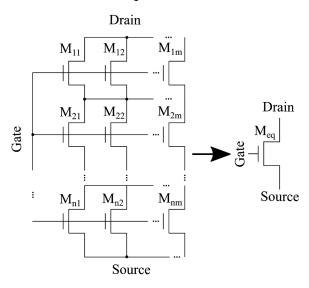

Além disso, alguns amplificadores operacionais de baixa tensão foram propostos nos últimos anos utilizando matrizes de transistores pequenos ao invés de um único transistor grande para reduzir os chamados efeitos de halo, que são causados por uma alteração na dopagem do material de fabricação dos transistores com o intuito de reduzir os efeitos de canal curto dos transistores (FERREIRA; SONKUSALE, 2014; ZHAO et al., 2015; GRASSO et al., 2015). Isso pode levar o projeto a ter mais variáveis livres, como o número de linhas e colunas nessas matrizes de transistores.

Nos casos de circuitos mais complexos, uma possibilidade é o uso de algoritmos baseados em alguma heurística para a escolha dos valores para as variáveis. Esses algoritmos podem processar muitas especificações de projeto simultaneamente (DEY et al., 2014). Dessa forma, o uso de algoritmos heurísticos são considerados uma boa solução para projeto dos CIs analógicos.

Heurísticas são utilizadas para resolver problemas de grande tamanho com muitos critérios a serem considerados (TALBI—ANTONIO; ALBA, 2006). Elas podem ser adaptadas para atender aos requisitos específicos do problema. Mesmo que não garantam encontrar a solução ótima, elas fornecem boa capacidade de encontrar uma solução aceitável (CHAN; TIWARI, 2007).

Na síntese baseada em otimização, o dimensionamento dos componentes é transformado em um problema de minimização de função que pode ser calculado através de métodos numéricos ou por simulação. Eles são baseados na introdução de um avaliador de desempenho dentro de um laço de otimização iterativa. A cada modificação dos valores das variáveis livres, a avaliação é realizada.

Sistemas de avaliação baseados em métodos numéricos ou equações muitas vezes consomem muito mais tempo de preparo, além de que as simplificações requeridas nas equações causam baixa precisão e incompletude. Os métodos baseados em simulação não se baseiam em equações analíticas, mas em simulações do tipo SPICE para avaliar os desempenhos do circuito no processo de otimização, o que resulta em uma maior precisão.

Algumas técnicas de otimização são mais diretas, preocupadas em achar apenas uma solução, caindo com frequência em ótimos locais, como os algoritmos gulosos. Outras se destinam a pesquisar com mais cuidado o espaço de soluções, na tentativa de obter resultados mais próximos do ótimo. Algumas heurísticas apresentadas na literatura são Pesquisa Local (AARTS; LENSTRA, 2003), Simulated Annealing (SA) (SIARRY et al., 1997), Tabu Search (TS (GLOVER, 1989), etc.

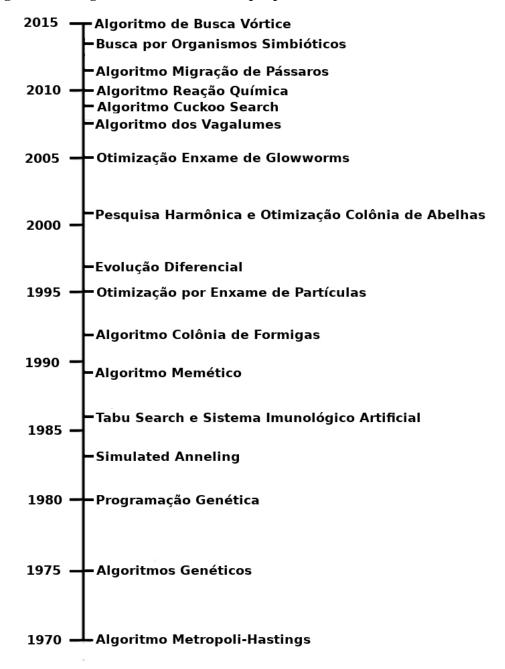

A maioria dos problemas de otimização de projeto de circuito exigem simultaneamente diferentes tipos de variáveis, funções objetivo e de restrição na sua formulação. Os procedimentos de otimização acima mencionados requerem um longo tempo de computação quando o problema apresenta um grande espaço de busca e um grande número de objetivos a serem alcançados. Nos últimos anos, foram propostos novos algoritmos de otimização heurística, muitos deles inspirados na natureza. A ideia por trás desses algoritmos é se inspirar no comportamento coletivo dos sistemas descentralizados e auto-organizados (VURAL, 2012). A técnica de se inspirar em comportamento coletivo das espécies é conhecida como Swarm Intelligence (SI) (BONABEAU; DORIGO; THERAULAZ, 1999). Em muitos trabalhos eles demonstraram alcançar melhores resultados comparados às estratégias que utilizam um único agente na exploração do espaço de busca. Algumas heurísticas bio-inspiradas ainda não foram amplamente utilizadas na otimização de CIs analógicos.

#### 1.1 OBJETIVO

Este trabalho tem por objetivo utilizar heurísticas bio-inspiradas na otimização de amplificadores operacionais (amp-ops) de forma automática. Para isso, são utilizadas três heurísticas: Particle Swarm Optimization (PSO), Firefly Algorithm (FA) e Cuckoo Search (CS). Estas heurísticas são utilizadas pelo fato de apresentarem bons resultados em otimizações de uma série de problemas e não serem, até então, amplamente utilizadas no processo de otimização de CIs analógicos. A ideia é analisar o comportamento dessas heurísticas no projeto de CIs analógicos. Além disso, outro objetivo do trabalho é propor uma estratégia que permita utilizar como variáveis livres as dimensões das matrizes de transistores utilizadas em alguns amplificadores de baixa tensão, desenvolvendo um algoritmo capaz de gerar sub-circuitos de forma automática em cada iteração da heurística de acordo com o número de transistores em série e em paralelo de cada matriz. Técnicas automáticas de design de amp-ops que considerem essas dimensões como variáveis livres foram pouco exploradas na literatura.

Para que os objetivos sejam atendidos, é necessário, a partir da determinação das especificações a serem atendidas pelo circuito, explorar o espaço de projeto a fim de encontrar uma solução que atenda as restrições a fim de gerar um circuito otimizado, isto é, de tamanho reduzido, com baixa dissipação de potência e que satisfaça as demais especificações desejadas.

São comparadas três heurísticas, PSO, FA e CS, no projeto de um OTA (Operational Transconductance Amplifier) Miller. Em seguida, a heurística CS é utilizada para dimensionar outros dois amplificadores, um do tipo telescopic e um de baixa tensão alimentado pelo substrato com capacitor Miller.

# 1.2 ORGANIZAÇÃO DO TRABALHO

A sequência desse trabalho está organizada como segue. No segundo capítulo são apresentadas as etapas necessárias para a concepção de um CI analógico funcional, focando nas características do processo de dimensionamento e apresenta também os modelos elétricos dos CIs dimensionados. Nesse capítulo também é realizada uma revisão da literatura acerca de métodos para o design de CIs analógicos. No capítulo 3 é demostrado o fluxo básico da ferramenta utilizada, como é realizada a otimização, principais funções, *testbenches* para determinar os valores das especificações e como é realizado o cálculo da função custo. No capítulo 4 são apresentadas as heurísticas utilizadas para otimizar os circuitos, o critério de parada utilizado e um estudo sobre os valores iniciais para as variáveis livres a serem trabalhadas nas heurísticas. O capítulo 5 apresenta os circuitos dimensionados neste trabalho e os resultados obtidos para cada um deles, como valor das especificações. Por fim, no capítulo 6 é apresentada a conclusão sobre o trabalho desenvolvido.

# 2 PROJETO DE CIRCUITOS INTEGRADOS ANALÓGICOS

Neste capítulo é apresentado o fluxo necessário para a concepção de um CI analógico, desde o início do projeto até a fase de prototipação. São apresentadas as sub-divisões do projeto, isto é, todas as fases que devem ser realizadas para a criação de um CI funcional. Também é descrito como o projeto de um CI pode ser transformado em um projeto automático utilizando otimização. Por fim, é realizada uma revisão bibliográfica acerca de trabalhos cujo foco é o dimensionamento de CIs analógicos de forma automática.

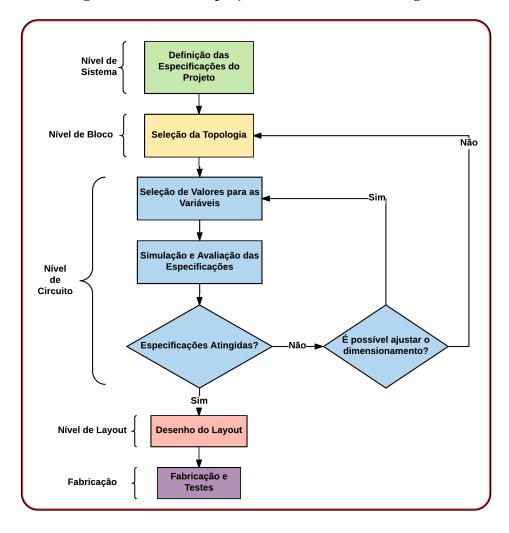

De acordo com Barros, Guilherme e Horta (2007), para assegurar o funcionamento dos circuitos integrados analógicos, deve-se seguir cinco níveis hierárquicos de projeto:

- 1. Nível de sistema: Neste estágio de desenvolvimento, as especificações requeridas pelo circuito e a tecnologia do processo de fabricação são definidos;

- Nível de bloco: Neste estágio, descrições em alto nível dos blocos básicos são efetivamente traduzidos para uma arquitetura de blocos funcionais requeridos para realizar o comportamento especificado pelo sistema;

- 3. Nível de circuito: Nesta fase realiza-se um processo de otimização para cada bloco básico analógico, onde a otimização é um processo iterativo para determinar as dimensões físicas em nível de dispositivo, por exemplo, as dimensões dos transistores. A tolerância do projeto deverá ser obtida levando em conta as variações ambientais e do processo de fabricação para garantir que o CI atenderá às especificações após o processo de fabricação. Para isso pode-se utilizar análise de Monte Carlo ou de Corners (pior caso). As especificações elétricas e de desempenho requeridas do circuito final são verificadas usando um simulador SPICE;

- 4. Nível de leiaute: Nesse estágio, os blocos básicos otimizados no passo anterior são representados de forma física. Leiaute é um conjunto de formas geométricas que devem obedecer às regras de projeto especificadas pelo processo de fabricação;

- 5. Fabricação e teste: Nesse estágio, o projeto do leiaute produzido na etapa anterior é enviado para fabricação e o CI é finalmente produzido. O teste e validação são passos fundamentais para assegurar a operação correta do circuito integrado e, assim, um sistema de caracterização elétrica adequado deve ser definido.

Na figura 1 pode ser observada uma abstração dos níveis hierárquicos de projeto proposto por Barros, Guilherme e Horta (2007).

No nível de sistema uma topologia de circuito é escolhida de acordo com as especificações desejadas. A topologia é escolhida com base no conhecimento do projetista. A partir da escolha da topologia, é realizada a definição da arquitetura dos

Figura 1 – Níveis de projeto de um circuito analógico.

Adaptado de Barros, Guilherme e Horta (2007)

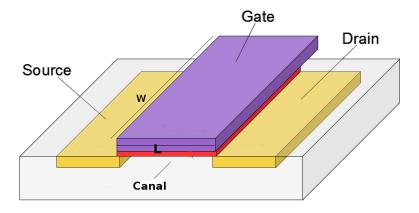

blocos que irão compor o circuito. Já no nível de circuito, os transistores do circuito devem ser dimensionados. Neste dimensionamento determina-se o comprimento e largura do gate do transistor, como mostrado na figura 2.

Para um primeiro dimensionamento, normalmente o projetista faz uso de equações aproximadas, como equação da corrente  $I_D$  do modelo quadrático para transistores CMOS (HOLBERG; ALLEN, 2002; SEVERO; GIRARDI, 2011).

Após o dimensionamento inicial, o circuito deve ser simulado e os resultados comparados com as especificações desejadas. Isto é realizado através de simulações do tipo SPICE. Caso as especificações desejadas não sejam atingidas, deve-se refazer o processo de dimensionamento. Se não for possível atingir as especificações redimensionando o circuito, deve-se escolher outra topologia de circuito. Se as especificações forem atingidas, então pode-se progredir ao nível de leiaute.

Na fase de leiaute o projetista deve adotar estratégias que permitam desenhar o CI de forma que ele tenha baixa variabilidade de parâmetros após a fabricação, ou

Figura 2 – Estrutura física de um transistor em tecnologia CMOS.

Adaptado de (LEE et al., 2009)

seja, se comporte como o esperado (SEVERO; GIRARDI, 2011). Após a fase de leiaute, o circuito deve novamente ser simulado, uma vez que agora ele possui elementos como capacitâncias e resistências.

O projeto de um CI analógico possui uma série de etapas. Em todas essas etapas é necessário tomar decisões e validar o CI. Normalmente todas as decisões são tomadas de acordo com a experiência do projetista. No dimensionamento dos componentes, considerada a parte mais crítica, geralmente o projetista realiza a mudança de apenas um parâmetro ou apenas uma das dimensões de um dos transistores do circuito por vez.

Encontrar um ponto de polarização dos circuitos que atinja as especificações do projeto requer muitas iterações de redimensionamento e simulações. Cada vez que um componente é redimensionado, deve-se realizar a simulação elétrica a fim de verificar se as especificações de projeto foram atingidas e também se não foi degradado nenhum dos demais objetivos do projeto (MORETO et al., 2012).

No dimensionamento dos transistores, o uso de equações simplificadas na maioria das vezes leva a resultados que não retratam o real funcionamento do circuito. Outro problema na etapa de dimensionamento do circuito, é que muitas vezes redução de área e potência consumida acabam sendo considerados objetivos secundários. O objetivo principal é produzir um circuito que atinja as especificações do projeto.

Para que o circuito dimensionado por meio de simulação fique o mais próximo possível de um circuito fabricado, deve-se considerar no dimensionamento as variações do processo de fabricação.

### 2.1 PROJETO AUTOMÁTICO DE ICS ANALÓGICOS

O processo de dimensionamento do circuito baseado apenas na experiência e conhecimento do projetista possui algumas desvantagens, pois é necessário que para

cada diferente topologia seja criado um novo plano de projeto (SEVERO; GIRARDI, 2011).

Outra possibilidade para dimensionar um CI analógico é transformar o dimensionamento em um problema de otimização combinatória. Nessa estratégia algum método de otimização é utilizado para explorar o espaço de projeto, isto é, a variação da dimensões dos componentes é realizada de forma automática de acordo com os valores obtidos para as especificações a cada iteração. Os métodos baseados em otimização podem ser baseados em equações ou em simulação elétrica (BARROS; GUILHERME; HORTA, 2007).

Os modelos baseados em equações tendem a ser mais rápidos, uma vez que não é necessária uma simulação elétrica completa, no entanto, as simplificações necessárias nas equações podem levar a uma menor precisão. Além disso, não é possível obter todas as especificações.

Os métodos baseados em simulação elétrica utilizam simuladores elétricos do tipo SPICE para avaliação do circuito. Para essa simulação, são utilizados modelos elétricos fornecidos pelas empresas de fabricação dos CIs. Apesar desse modelo consumir um maior tempo computacional, uma vez que é necessário realizar diferentes simulações para medir as várias especificações, este método é mais preciso, pois é baseado em modelos complexos para a modelagem dos dispositivos.

A utilização de simulação elétrica do tipo SPICE permite que sejam analisadas de forma confiável qualquer especificação do circuito. Isto dá ao modelo de otimização uma maior flexibilidade. Além disso, este modelo de projeto permite realizar a análise da produtividade do circuito através da análise de Monte Carlo, por exemplo (SEVERO, 2012). A análise da produtividade pode ser considerada já no processo de otimização, e não realizada apenas no final do dimensionamento (DOMANSKI, 2016).

Uma etapa também muito importante no processo de dimensionamento automático de um CI é a escolha do método de otimização. Existe um grande número de métodos que podem ser utilizados.

A escolha do método de otimização deve ser estudada a fim de que o modelo escolhido consiga atingir uma solução que atenda as especificações desejadas e permita considerar outros objetivos como redução da área e da potência. Existem diferentes tipos de métodos de otimização, como métodos exatos, métodos heurísticos entre outros.

Os métodos de otimização heurísticos nem sempre garantem a solução ótima, pois são métodos estocásticos. No entanto, quando o espaço de busca é não linear e muito grande, eles são uma boa estratégia para a busca de uma solução (GIUNCHIGLIA et al., 2001).

Uma vantagem dos métodos heurísticos é que muitos deles não dependem da solução inicial, dessa forma, não é necessário um plano de projeto para determinar um dimensionamento inicial do circuito. No capítulo 4 são apresentados diferentes métodos

de otimização inspirados em inteligência das espécies.

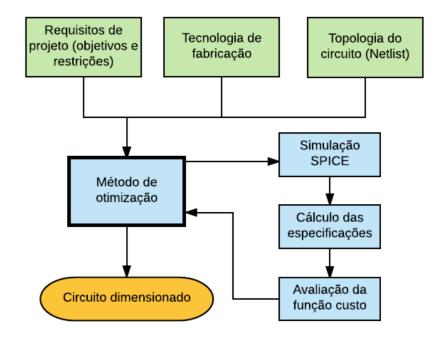

Para o dimensionamento automático de um circuito analógico utiliza-se geralmente ferramentas que recebem como entrada informações a respeito do circuito e das especificações desejadas e então é realizada a otimização através de um ciclo de avaliação e mudança de parâmetros. O fluxo de uma ferramenta iterativa de otimização com a avaliação de cada solução pode ser resumido como o mostrado na figura 3.

Especificações

Método de Otimização

Circuito

Dimensionado

Avaliação da

Performance

Avaliação da

Performance

Figura 3 – Fluxo básico de um modelo baseado em otimização.

Fonte: Autor.

#### 2.2 TRABALHOS RELACIONADOS

Diferentes trabalhos foram realizados com o intuito de propor técnicas que auxiliem no projeto e na redução do tempo de dimensionamento dos CIs analógicos. Alguns trabalhos buscam utilizar algoritmos baseados em heurísticas de otimização para a definição dos parâmetros do circuito, outros trabalhos tem como foco propor sistemas de representação das especificações do circuito como equações para tornar o processo de otimização mais rápido. Diversos trabalhos são encontrados na literatura a respeito dessas linhas. Neste capítulo é realizada uma revisão bibliográfica sobre alguns trabalhos que propõem a aplicação de métodos heurísticos da área de inteligência artificial (IA) na otimização de circuitos integrados analógicos.

Vários sistemas de projeto foram propostos para automatizar o projeto de blocos analógicos. Os trabalhos encontrados podem ser classificados em duas categorias: baseados no conhecimento e baseados em otimização.

#### 2.2.1 MÉTODOS BASEADOS NO CONHECIMENTO

As primeiras estratégias de automação, propostas há cerca de 30 anos, tentaram sistematizar o projeto usando um plano derivado do conhecimento (LOURENÇO; HORTA, 2012).

A ideia básica da abordagem baseada no conhecimento é traduzir a experiência do projetista em regras de síntese que utilizam equações simplificadas. O objetivo principal é representar as especificações do circuito através de equações que permitam calcular as dimensões dos componentes de forma a atender aos requisitos.

Alguns dos sistemas relatados na literatura que seguem esta abordagem podem ser vistos em Degrauwe et al. (1987), Onodera, Kanbara e Tamaru (1990) e El-Turky e Perry (1989).

A principal vantagem dessa abordagem é o curto tempo de execução. Por outro lado, criar um plano de projeto é difícil e demorado, além de que é necessário realizar frequentes mudanças nas equações para mantê-las atualizadas conforme a tecnologia evolui. Segundo Lourenço e Horta (2012), a abordagem baseada no conhecimento foi aplicada com sucesso moderado. Além disso, a precisão da solução muitas vezes não é satisfatória, uma vez que força as equações analíticas do projeto a serem simples (JAFARI et al., 2010).

# 2.2.2 MÉTODOS BASEADOS EM OTIMIZAÇÃO

A abordagem de projeto baseada em otimização utiliza um algoritmo para definir as dimensões do circuito. A otimização baseia-se na avaliação do circuito a cada iteração, que pode ser baseado em equações ou baseada em simulação elétrica.

Nos métodos de otimização baseados em equações, os sistemas usam modelos simplificados para prever o comportamento e desempenho do dispositivo dentro do ciclo de otimização (JAFARI; BIJAMI; ZEKRI, 2010). Segundo Lourenço e Horta (2012), o ponto forte dos métodos baseados em equações é o curto tempo de avaliação, tornando-os, assim como as abordagens baseadas em conhecimento, extremamente adequadas para derivar projetos simples em que não sejam consideradas muitas especificações.

Em Hershenson, Boyd e Lee (1998) alguns circuitos amp-op são otimizados usando Programação Geométrica (GP). O tempo de execução é na ordem de poucos segundos. Os resultados atingidos são comparados com os do simulador HSPICE e mostram que o sistema de equações atinge resultados muito próximos ao do simulador. No entanto, a aplicação do modelo é bastante difícil de derivar para novos circuitos. Essa

abordagem possui baixa precisão e limita as soluções em algumas regiões de operação do circuito (SEVERO et al., 2012).

A outra maneira é usar um simulador elétrico do tipo SPICE para avaliar o circuito com um modelo completo. Essa alternativa fornece melhor precisão, mas exige maior poder computacional.

Na Tabela 1 é mostrada uma relação de alguns trabalhos relacionados baseados em otimização, contendo de forma breve algumas informações como método de otimização utilizado, circuito dimensionado e sistema de avaliação das especificações do circuito.

|  | sobre otim |  |  |

|--|------------|--|--|

|  |            |  |  |

|  |            |  |  |

| Autor - ano            | Circuito<br>Otimizado                         | Método de<br>Otimização | Sistema<br>Avaliador | Tecnol. |

|------------------------|-----------------------------------------------|-------------------------|----------------------|---------|

| (JAFARI et al., 2010)  | amp-op de<br>dois estágios                    | GA                      | Equações             | 0.18 μm |

| (JAFARI et al., 2012)  | amp-op de<br>3 estágios                       | NHSFL                   | Equações             | 0.18 μm |

| (YENGUI et al., 2012)  | amp de transimpedância<br>e driver óptico     | GA e SQP                | Spectre              | 0.18 μm |

| (BARRA et al., 2012)   | amp-op de dois estágios<br>Miller             | MOGA                    | Equações             | 0.18 μm |

| (SEVERO et al., 2012)  | amp-op diferencial<br>e <i>folded cascode</i> | SA                      | HSPICE               | 0.18 μm |

| (DE et al., 2016)      | amp-op de dois estágios<br>e comparador       | СВС                     | Equações             | 0.35 μm |

| (DEHBASHIAN, 2017)     | amp-op de dois estágios                       | GSA-PSO                 | HSPICE               | 0.25 μm |

| (SASIKUMAR, 2017)      | amp-op de dois estágios                       | PSO-SA                  | Equações             | 0.35 μm |

| (MALLICK et al., 2017) | amp-op diferencial e<br>de dois estágios      | GSA e PSO               | Spectre              | 0.35 μm |

| (VURAL, 2012)          | amp-op diferencial e<br>de dois estágios      | PSO                     | Equações             | 0.35 μm |

| (HORTA, 2012)          | amp-op folded cascode                         | Otimização evolutiva    | HSPICE               | 0.18 μm |

Jafari et al. (2010) utiliza algoritmos genéticos para realizar o dimensionamento automático de circuitos integrados analógicos. A principal parte do trabalho é o dimensionamento da largura e comprimento do gate dos transistores que compõem o circuito, valores de resistores, capacitores e tensão e corrente de polarização. O Algoritmo Genético é utilizado juntamente com uma avaliação baseada em equações para produzir uma ferramenta que determine os tamanhos de dispositivos em um circuito analógico. O software pode otimizar os tamanhos do dispositivo considerando os objetivos e restrições impostas. Após o dimensionamento de um amp-op de dois estágios, o circuito é simulado usando o programa HSPICE com processo de 0.18 μm. O trabalho demonstra a eficiência dos algoritmos genéticos na determinação dos tamanhos dos dispositivos

em um circuito analógico. Porém, o uso de equações simplificadas, apesar de acelerar a análise de desempenho do circuito em cada iteração, acarreta a perda de precisão, pois o uso de equações dificilmente reflete o funcionamento do dispositivo na prática.

Em Jafari et al. (2012) é proposto um algoritmo denominado NHSFL (New Hybrid Suffled Frog Leaping) para dimensionar dois amplificadores operacionais em tecnologia  $0.18~\mu m$ , um Miller com capacitores aninhados de três estágios de ganho denominado NMC e outro chamado DPZCC (*Double Pole-Zero Cancellation compensated amp-op*). Esses amplificadores apresentam 11 e 18 transistores, respectivamente. Os circuitos são avaliados através de equações. As variáveis livres do algoritmo representam o comprimento e largura do gate dos transistores, além dos valores de capacitância do circuito. Os resultados do dimensionamento de ambos os amplificadores atingem as especificações desejadas para os circuitos. Os resultados são comparados para os mesmos circuitos com os algoritmos genéticos e algoritmo imperialista competitivo. A comparação mostra que o algoritmo proposto atinge melhores valores considerando desempenho e tempo de design.

No trabalho de Yengui et al. (2012) é proposto um algoritmo híbrido obtido pela combinação do algoritmo genético (GA) com programação sequencial quadrática (SQP). O GA é o principal otimizador, enquanto o SQP é usado para refinar mais os resultados. O algoritmo é aplicado para otimizar dois circuitos: um amplificador de transimpedância (TIA) e um driver óptico em tecnologia 0.18 μm, que são parte de uma rede ótica on-chip (ONoC). Os circuitos apresentam 12 e 8 variáveis livres, respectivamente. O artigo não demonstra os valores de cada especificação dos circuitos. Os resultados são comparados através de uma figura de mérito com o projetos dos mesmos circuitos utilizando o algoritmo SQP, em que o desempenho é determinado através do simulador Spectre.

Em Barra et al. (2012) é proposta uma metodologia de otimização de ampops utilizando MOGA (Algoritmo genético multiobjetivo). O algoritmo é utilizado para realizar a variação dos parâmetros do circuito, como dimensões do gate dos transistores, valor de capacitância e corrente de polarização. Em cada iteração do algoritmo é realizada uma avaliação do circuito através do uso de equações. Para avaliar a abordagem proposta, é realizada a otimização de um amp-op de dois estágios do tipo Miller em tecnologia 0.18 μm. Os objetivos no projeto são maximizar o GBW (ganho por largura de banda) e minimizar a potência dissipada. A otimização considera 14 variáveis livres. Após a execução, é realizada uma simulação elétrica no simulador Spectre e os resultados são comparados entre os obtidos pelas equações, pela simulação elétrica e apresentados em Jafari et al. (2010).

O trabalho publicado por Severo et al. (2012) apresenta o dimensionamento automático de um amplificador diferencial e um amplificador *folded cascode* utilizando o algoritmo Simulated Annealing para ajustar os parâmetros dos transistores do circuito.

Para o amplificador diferencial deseja-se maximizar o ganho e o intervalo em modo comum de entrada (ICMR) considerando outras especificações como restrições, como tamanho máximo de área, margem de fase e ganho por largura de faixa (GBW). O projeto do amplificador *folded cascode* considera 15 variáveis livres representando as dimensões do gate de 6 transistores, duas tensões de referências e a corrente de polarização do circuito. Para esse amplificador deseja-se minimizar a potência consumida e a área do circuito enquanto as restrições são ganho em baixas frequências (Av0), GBW, margem de fase e tempo de resposta (*slew rate - SR*). Os circuitos são avaliados através de simulação elétrica do tipo SPICE. Uma função custo é apresentada para representar o desempenho do circuito, no qual deseja-se minimizá-la. Os circuitos são implementados em tecnologia CMOS  $0.18~\mu m$  com uma tensão de alimentação de  $1.8~\rm V$ . A metodologia de projeto é implementada em Matlab e o simulador Synopsys HSPICE é utilizado para simulação do circuito.

Em Mallick et al. (2017) propõe-se um algoritmo híbrido baseado em população denominado algoritmo de busca gravitacional (GSA) combinado com otimização por enxame de partículas (PSO) (GSA-PSO) para projetar dois circuitos analógicos, um amplificador diferencial e um amplificador operacional de dois estágios em tecnologia CMOS de 0.35 µm. Os circuitos são otimizados utilizando-se 14 e 19 variáveis livres, respectivamente, representando as dimensões do gate dos transistores, corrente de polarização, capacitor de carga e um capacitor de acoplamento (apenas no amplificador operacional). O objetivo da otimização é minimizar a área do gate dos transistores e o consumo, além de maximizar o ganho em baixas frequências. São utilizadas equações para a avaliação do circuito durante o processo de otimização. Após o dimensionamento é realizada simulação SPICE em software Cadence IC 5.1. Os resultados obtidos no trabalho através de simulação elétrica mostram que o uso da estratégia híbrida levou a melhores resultados em relação a outros algoritmos da literatura em termos de velocidade de convergência, especificações de projeto e parâmetros de desempenho dos amplificadores. Os resultados obtidos mostram que foi possível obter um circuito de menor área e melhor desempenho como ganho e dissipação de potência em comparação com outros algoritmos. Segundo os autores, a maior dificuldade nesse trabalho é o ajuste dos parâmetros dos algoritmos GSA e PSO.

No trabalho de Vural (2012) foi utilizada a heurística PSO para o dimensionamento de um amplificador diferencial com espelho de corrente e um amplificador operacional de dois estágios. Os circuitos foram projetados utilizando tecnologia TSMC de 0.35 μm. Para a otimização são utilizadas equações e o objetivo é apenas reduzir a área. Após o processo de dimensionamento, os parâmetros de projeto resultantes são utilizados em simulador SPICE para validar os valores das especificações de projeto. São necessários alguns ajustes manuais para que se atenda a todas as especificações dos projetos. Os resultados alcançados satisfazem todas as especificações de projeto e a área

de ambos os circuitos é minimizada em comparação com outros métodos como GA e Busca Tabu.

Em Lourenço e Horta (2012) é proposta uma ferramenta para realizar a síntese automática de circuitos analógicos utilizando otimização evolutiva. Como caso de estudo é realizado o dimensionamento de um amp-op *folded cascode* com 15 variáveis livres e os objetivos são minimizar área e potência. A avaliação da performance é realizada através de simulação SPICE no simulador HSPICE. O projeto também leva em consideração a produtividade, realizada através de análises de corners. Nessa análise o circuito é simulado considerando as piores hipóteses em que o circuito pode funcionar de acordo com as variações de parâmetros de processo, como por exemplo tensão de alimentação, temperatura, etc.

Em De et al. (2016) são dimensionados dois CIs, um comparador de dois estágios e um amp-op de dois estágios folded-cascode utilizando um algoritmo proposto recentemente denominado Otimização de Corpos Colidentes (Colliding Bodies Optimization - CBO). O CBO é um algoritmo multiagente que não depende de nenhum parâmetro de controle interno. O principal objetivo desse trabalho é otimizar o dimensionamento dos gates dos transistores para reduzir as áreas ocupadas pelos circuitos e obter melhores parâmetros de desempenho dos circuitos. Algumas das especificações consideradas no projeto são Av0, margem de fase, ICMR, potência dissipada, tempo de resposta e etc. A tecnologia utilizada é  $0.35~\mu m$  com uma tensão de alimentação de 5 V. No comparador são utilizadas 7 variáveis livres, representando a largura e comprimento do gate dos transistores e um resistor. Para o amp-op a otimização é realizada utilizando 17 variáveis livres representando as dimensões dos gates dos transistores, dois resistores e um capacitor. A otimização é realizada utilizando equações e após o dimensionamento o circuito é simulado para validar seu funcionamento.

No trabalho de Dehbashian (2017) é proposto um algoritmo híbrido utilizando o Algoritmo de Busca Gravitacional (GSA) e PSO para dimensionar um amp-op de dois estágios em tecnologia de  $0.25~\mu m$ . O objetivo da otimização é reduzir a área e consumo do CI. A otimização é realizada considerando 12 variáveis livres representando as dimensões do gate de 5 transistores, corrente de polarização e tamanho de um capacitor. O circuito é alimentado com  $1.8~\rm V$  e as especificações consideradas são ganho em baixas tensões, margem de fase, consumo de potência, *output swing* entre outros. Os resultados são comparados com outros trabalhos e atingem melhores resultados principalmente para potência e área do gate.

Em Sasikumar (2017) é usada uma implementação híbrida com PSO e GA para o dimensionamento de um amp-op de dois estágios em tecnologia  $0.35~\mu m$ . O objetivo é reduzir a área e potência dissipada pelo circuito. O sistema avaliador no ciclo de otimização é baseado em equações e após o circuito dimensionado é realizada simulação no simulador Cadence IC 5.1. O sistema é modelado como um problema de otimização

com nove variáveis livres representando as dimensões do gate dos transistores e uma capacitância. Os resultados são comparados com os obtidos no dimensionamento do mesmo amp-op utilizando apenas o PSO e demonstram que os algoritmos utilizados atingiram melhores resultados para a maioria das especificações do amplificador.

### 2.2.3 CONCLUSÃO

Neste capítulo foram apresentados os níveis hierárquicos para assegurar o funcionamento dos circuitos integrados analógicos, como nível de sistema, nível de bloco, nível de circuito, nível de leiaute e nível de fabricação e teste. Também foi apresentado o fluxo básico para o dimensionamento automático de CIs analógicos, transformando o processo de dimensionamento em um problema de otimização combinatória e fazendo o uso de um algoritmo heurístico para tal tarefa.

Também foi apresentada uma revisão bibliográfica sobre o projeto automático de circuitos integrados analógicos. Através deste estudo bibliográfico observou-se que diversos trabalhos buscam estudar métodos que auxiliem no projeto de CIs analógicos visando diminuir o tempo de design e aumentar a qualidade dos CIs projetados. Na maioria dos trabalhos descritos afirma-se que um projeto dependente apenas do conhecimento do projetista pode ser muito demorado e é bastante complexo quando o circuito possui um número grande de variáveis livres e várias especificações a serem atendidas. Um grande número de trabalhos recentes busca explorar o uso de inteligência artificial para realizar o dimensionamento do circuito. Alguns dos trabalhos verificam o comportamento de novos algoritmos para circuitos considerados básicos, enquanto em outros o foco é realizar o dimensionamento de circuitos mais complexos, com maior número de variáveis livres e número de restrições. Existe uma dificuldade de comparação entre os resultados de boa parte dos trabalhos pelo fato de que eles utilizam diferentes topologias de circuitos ou diferentes tecnologias de fabricação para a simulação ou cálculo da especificações.

### **3 A FERRAMENTA UCAF**

Este capítulo busca detalhar o funcionamento das principais partes da ferramenta utilizada para o dimensionamento automático de blocos analógicos deste trabalho. São listadas as informações que a ferramenta deve receber do usuário, como ela realiza a alteração dos valores para cada variável do circuito e como é realizada a simulação e avaliação das especificações.

Neste trabalho foi utilizada a ferramenta UCAF, desenvolvida em linguagem Matlab® por Severo (2012), com funcionalidades acrescentadas por Domanski (2016), no Grupo de Arquitetura de Computadores e Microeletrônica da Unipampa (GAMA).

A ferramenta UCAF baseia-se em uma metodologia de otimização utilizando heurísticas para pesquisar o espaço de projeto e simulação elétrica SPICE para avaliação do comportamento dos circuitos. Na figura 4 ilustra-se o fluxo básico dessa ferramenta.

Figura 4 – Fluxo de projeto da ferramenta UCAF.

Adaptado de Severo (2012)

O método de otimização recebe como entrada as especificações a serem atendidas pelo CI, as restrições do projeto, a tecnologia de fabricação e a descrição elétrica do circuito, chamada de *netlist*. Com essas informações, o método de otimização define valores para as variáveis livres do circuito, que representam as dimensões dos dispositivos, valores de capacitores, resistores e etc, e então realiza a simulação elétrica a fim de obter os valores das especificações e calcular a função custo, com base na equação 3.4. Com base na avaliação da função custo, o método de otimização atribui novos valores às variáveis do circuito com o intuito de buscar uma solução melhor. Esse ciclo se repete até que se

atinja uma solução considerada satisfatória, isto é, que atenda aos requisitos do projeto ou algum critério de parada definido pelo usuário.

A ferramenta UCAF é composta por vários módulos, como módulo principal, módulo de otimização, módulo de simulação elétrica, entre outros. Dessa forma, a manutenção e escalabilidade da ferramenta pode ser realizada de forma simples. Caso seja desejado utilizar uma nova heurística para realizar a otimização do circuito, é necessário alterar apenas o módulo de otimização.

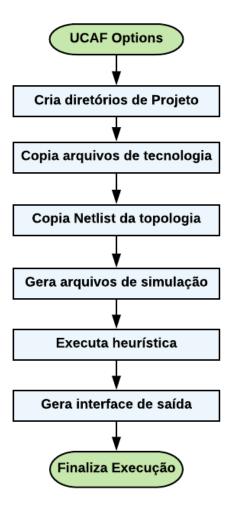

### 3.1 NÚCLEO PRINCIPAL

A ferramenta possui um núcleo onde o usuário ajusta as variáveis de configuração. O núcleo baseia-se na estrutura UCAF Options, que representa as configurações ajustadas na interface de entrada. A figura 5 demonstra de forma resumida o funcionamento do núcleo da ferramenta.

Figura 5 – Fluxograma de execução do núcleo da ferramenta.

Adaptado de Severo (2012)

As duas primeiras etapas apresentadas no fluxograma representam a preparação

3.1. Núcleo Principal 41

dos diretórios e arquivos necessários para a execução. É criado um diretório de projeto e neste diretório são copiados todos os arquivos necessários para a simulação do CI, como netlist, arquivos referentes a tecnologia e arquivos de simulação elétrica gerados. A partir disso, o algoritmo de otimização altera os valores dos parâmetros do circuito a fim de atingir as especificações. Com o circuito dimensionado, são gerados relatórios para o usuário contendo informações como tamanhos e valores para os parâmetros de cada dispositivo, valores atingidos para cada especificação e demais informações pertinentes.

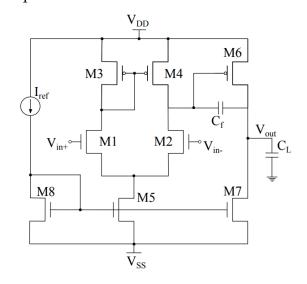

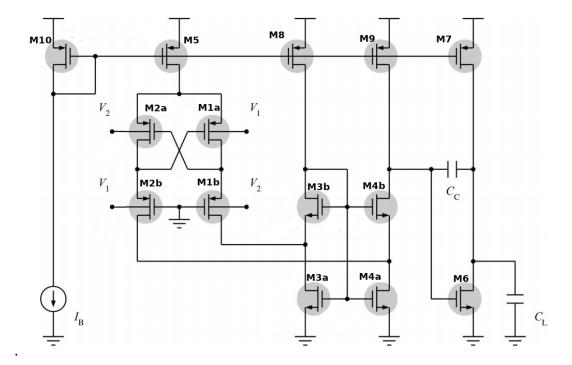

Por exemplo, para o dimensionamento do OTA Miller representado na figura 6, o usuário deve criar um netlist, como o demonstrado na figura 7, e informar à ferramenta o caminho desse arquivo representando o circuito.

Figura 6 – Esquemático de um OTA Miller em tecnologia CMOS

Fonte: Adaptado de Severo (2012)

As linhas iniciadas com um asterisco são interpretadas como comentário e, portanto, não são consideradas na ferramenta. Os parâmetros 'lr' e 'wr' representam o comprimento e a largura do gate dos transistores, respectivamente. Por exemplo, na linha 10 da figura, 'lr=L1\*1e-6' significa que comprimento do gate do transistor chamado 'x1' será de L1 micrômetros, sendo que L1 é uma variável alterada a cada iteração pela heurística de otimização e escrito em outro arquivo pela ferramenta, este arquivo se encontra no mesmo diretório e é importado para esse netlist. A mesma lógica é seguida para todos os outros 'lr', 'wr', IB e Cc. Dessa forma, a cada iteração do algoritmo é necessário alterar apenas o arquivo de parâmetros (mostrado na figura 8). Cada parâmetro é uma variável livre no processo de otimização.

Os valores das dimensões dos transistores são limitados pelo modelo do transistor disponível para simulação elétrica. A capacitância e a corrente devem possuir uma faixa limitada pela viabilidade desse valor para a posterior fabricação e bom

Figura 7 – Netlist representando o OTA Miller da figura 6.

```

*netlist representando o OTA Miller

2

*inclusão das bibliotecas com os modelos elétricos

3

4

.lib 'xh018/lp3mos/cr018gpii_v1d0.l' TT_RFMOS

.lib 'xh018/lp3mos/cr018gpii v1d0.l' stat noise

5

6

7

*Descricao elétrica

.subckt OTA_miller vp vn vdd vss vout

8

9

x1 2 vn 3 3 nmos_rf lr='L1*1e-6' wr='W1*1e-6'

10

x2 5 vp 3 3 nmos_rf lr='L1*1e-6' wr='W1*1e-6'

11

x3 2 2 vdd vdd pmos_rf lr='L3*1e-6' wr='W3*1e-6'

12

x4 5 2 vdd vdd pmos_rf lr='L3*1e-6' wr='W3*1e-6'

13

x5 3 4 vss vss nmos_rf lr='L5*1e-6' wr='W5*1e-6'

14

x6 vout 5 vdd vdd pmos rf lr='L6*1e-6' wr='W6*1e-6'

15

x7 vout 4 vss vss nmos_rf lr='L7*1e-6' wr='W7*1e-6'

16

x8 4 4 vss vss nmos rf lr='L5*1e-6' wr='W5*1e-6'

17

18

Ibias vdd 4 'IB*1e-6'

19

Cc 5 vout 'Cc*1e-12' IC=0

20

Cl vout 0 3p IC=0

21

22

.ends

```

funcionamento do circuito.

Uma vez gerados os valores para as variáveis livres do circuito, ele então é simulado e suas especificações são avaliadas através de uma série de *testbenches*, mostrados na seção 3.2. O simulador HSPICE é invocado pela ferramenta através de uma chamada de sistema contendo os arquivos de entrada e saída para a simulação. Na seção 3.2 é demonstrado um exemplo de arquivo de entrada representando um *testbench*.

# 3.2 ESPECIFICAÇÕES E TESTBENCHES

As especificações de um circuito representam o comportamento que se deseja que o circuito apresente. Nesta aplicação, é necessário que a otimização automática leve em conta todas elas. Para isso, o usuário deve informar quais são as especificações, os valores desejados para cada uma (limites mínimos e máximos aceitáveis) e quais delas são principais focos da otimização, ou seja, quais deseja-se minimizar o seu valor (ou maximizar).

As principais especificações para os amplificadores operacionais dimensionados no trabalho são as seguintes (SEVERO; GIRARDI, 2011):

Avo - representa o ganho em baixas frequências. Obtido através de análise no domínio da frequência em malha aberta, através de simulação CA.

Figura 8 – Exemplo de arquivo de parâmetro gerado pela ferramenta UCAF para o circuito da figura 6.

```

* Projeto_Miller Parameters File

.PARAM W1=6.900956e+00

.PARAM L1=3.062347e-01

.PARAM W3=8.0000000e+00

.PARAM L3=2.855465e-01

.PARAM W5=7.098635e+00

.PARAM L5=4.939068e-01

.PARAM W6=8.000000e+00

.PARAM L6=1.800000e-01

.PARAM W7=3.278318e+00

.PARAM L7=1.965620e-01

.PARAM IB=1.265602e+01

.PARAM Cc=9.633470e+00

```

- GBW produto ganho-largura de faixa. Obtido pela análise no domínio da frequência.

- PM é a margem de fase. Assim como o Avo e GBW, a margem de fase é obtida pela análise no domínio da frequência.

- SR velocidade de resposta. Para se obter esse valor é necessária uma análise no domínio do tempo, obtida por uma simulação transiente.

- ICMR tensão no modo comum de entrada. É realizada uma simulação CC (variação linear no nível de tensão ou corrente).

- OS Faixa de tensão de saída. É realizada uma simulação da faixa de tensão de saída do circuito durante a sua operação, obtida também através de simulação CC.

- Potência dissipada Calculada através de uma simulação do ponto de operação do circuito.

- Área de gate é calculada pela multiplicação da largura pelo comprimento do canal de cada transistor.

As especificações são divididas em dois tipos: as de restrição e as de otimização. Todas as especificações listadas podem ser de qualquer um dos dois tipos, conforme a configuração dada pelo usuário. As especificações de restrição são as que apresentam um intervalo de valores aceitáveis. Caso o valor obtido esteja fora desse intervalo, a solução é descartada. As de otimização não invalidam a solução alcançada e deseja-se

sempre minimizá-las (ou maximizar), como por exemplo o consumo de um CI, quanto menor, melhor . Esse conceito é detalhado na seção 3.4.

Para obtenção dos valores das especificações, são necessárias simulações elétricas utilizando diferentes análises: CA, CC e transiente. Os *testbenches* de medição, implementados com base em Allen et al. (1987), são mostrados nas seguintes seções.

### 1. Análise no domínio da frequência em malha aberta e potência dissipada

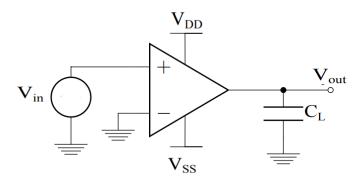

Este *testbench* é capaz de medir as características em malha aberta do circuito, como Av0, GBW, margem de fase e potência dissipada. O circuito utilizado para esta análise é mostrado na figura 9. A frequência da tensão senoidal de entrada é variada dentro de uma faixa, e a tensão de saída é calculada no domínio da frequência.

Figura 9 – Configuração de circuito para medição de características AC.

Fonte: Autor.

A ferramenta gera de forma automática os arquivos de netlist representando os *testbenches*, como demonstrado na figura 10.

### 2. Velocidade de resposta

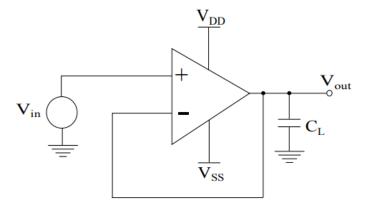

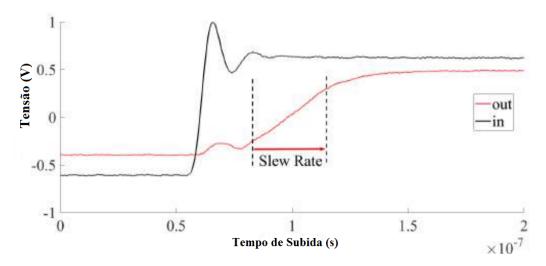

A velocidade de resposta (slew rate) do amplificador é medida através de uma simulação transiente para obter a taxa de variação da frequência no decorrer do tempo (dV/dt). O circuito da figura 11 pode ser utilizado para esse tipo de análise (SEVERO; GIRARDI, 2011). Deve-se gerar uma fonte quadrada na entrada do circuito e verificar a alteração na tensão de saída. O objetivo da medição é verificar a taxa de alteração do nível de saída do amplificador operacional

Para obter a taxa de variação do op-amp, a taxa de alteração do sinal de saída deve ser medida nas bordas de subida e descida. A inclinação da curva (subida ou descida) é calculada na região mais linear do gráfico. A figura 12 mostra um exemplo dessa medição realizada de forma elétrica.

Figura 10 – Netlist gerado pela ferramenta representando o circuito da figura 9.

```

Title: Projeto_Miller OpenLoopAC_type1

*Netlist Generated by UCAF Framework

3

4

5

.OPTIONS POST=1

.OPTIONS POST VERSION=9601

7

8

*Include Parameters

9

.include Projeto_Miller.par

10

*Include Netlist

11

12

.include Miller_Netlist.txt

13

14

*Circuit Simulations

15

VDD VDD 0 9.000000e-01

16

VSS VSS 0 -9.000000e-01

17

X1 VINP 0 VDD VSS OUT OTA_miller

VINP VINP 0 DC 0 AC 1

18

19

.AC DEC 100 1 1G

.DC VINP 0.000000e+00 9.000000e-01 9.000000e-01

20

21

.END

```

Figura 11 – Configuração de circuito para medição do slew rate.

Fonte: Autor.

### 3. Tensão de entrada em modo comum

Para medir a tensão de entrada em modo comum (ICMR) utiliza-se a mesma configuração de circuito para medir o slew rate, mostrada na figura 11. Para esta medição, uma onda de formato triangular é usada como entrada no circuito e observa-se a região linear da relação  $V_{in}xV_{out}$  do circuito, como mostra a figura 13.

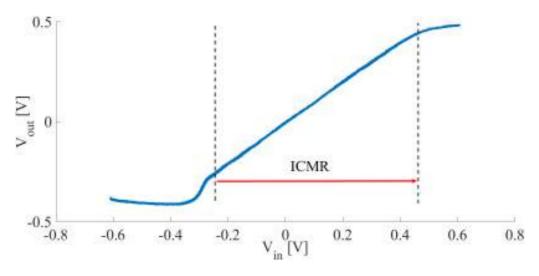

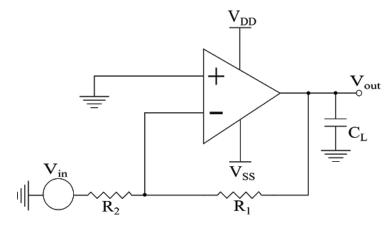

### 4. Faixa de tensão de saída

A faixa de tensão de saída, ou output swing (OS), pode ser obtida através de uma simulação de amplificação de forma que seja possível saturar o sinal de saída.

Figura 12 – Resposta de saída para medição de taxa de variação.

Fonte: Autor.

Através da faixa linear e de saturação do sinal de saída, os valores máximos e mínimos da excursão do sinal de saída são obtidos. A figura XXX mostra o gráfico  $V_{in}xV_{out}$  onde o OS é medido nos pontos máximo e mínimo onde a saída ainda é linear.

A configuração utilizada na ferramenta para a medição do OS é mostrada na figura 15 (SEVERO, 2012).

Para que a ferramenta possa obter os valores de cada especificação na simulação, é utilizado um *toolbox* Hspice para Matlab, que é um conjunto de funções fornecidas

Figura 14 – Configuração de circuito para medição do output swing.

Figura 15 – Medição  $V_{in}xV_{out}$ para extração do output swing.

Fonte: Autor.

que permitem visualizar e manipular os resultados gerados na simulação.

# 3.3 BLOCO DE OTIMIZAÇÃO

O bloco de otimização é um dos principais blocos da ferramenta. Ele é o bloco responsável por definir os valores e dimensões para os componentes do circuito. Para isso, ele utiliza um algoritmo baseado em heurística que gera valores para as variáveis do circuito.

As soluções geradas para o circuito devem sempre estar dentro das dimensões máximas e mínimas permitidas pela tecnologia utilizada. A partir dos valores gerados é realizada a simulação e o cálculo da função custo com base nos valores obtidos para as especificações. Baseado na função custo, o algoritmo de otimização altera os valores

para as variáveis. A função custo utilizada para avaliação do circuito pelas heurísticas da ferramenta é apresentada na seção 3.4

Na ferramenta UCAF em versões anteriores foram adicionadas as heurísticas dos Algoritmos Genéticos (GA) e Simulated Annealing (SA), ambas por Severo (2012), e PSO, desenvolvida por Domanski (2016), utilizada nesse trabalho e apresentada na seção 4.4.

# 3.4 FUNÇÃO CUSTO

A função custo (ou função de aptidão) tem grande importância no processo de otimização. Ela deve ser formulada de forma a refletir a qualidade da solução.

É muito importante que a função custo consiga diferenciar na proporção correta as melhores das piores soluções. Se houver pouca precisão em diferenciar as soluções boas das más, todo o processo de otimização será comprometido, uma vez que uma boa solução pode ser colocada de lado durante a execução do algoritmo, podendo levar o mesmo a explorar regiões não promissoras e a gastar mais tempo de computação (RAZAVI, 2001).

Neste trabalho a função custo leva em consideração tanto as especificações que devem ser otimizadas quanto as de restrição.

Dado um conjunto de funções de desempenho do circuito (especificações de projeto)  $\mathbf{Y}(\mathbf{r},\mathbf{q}) = \{S_1,S_2,...,S_s\}$  que depende de um conjunto de valores de parâmetros de projeto  $\mathbf{r}$  e de um conjunto de valores de parâmetros de tecnologia  $\mathbf{q}$ . S é uma especificação individual e s é o número de especificações de projeto. As funções de desempenho para um OTA sao as apresentadas na seção 3.2 (Av0, GBW, SR, potência dissipada, etc). Os parâmetros de projeto são as variáveis livres que o designer pode manipular para projetar o circuito, como dimensões do gate dos transistores, número de transistores unitários em série e em paralelo, correntes de referência, valores de capacitores, etc. Os parâmetros da tecnologia incluem informações sobre o modelo elétrico (como espessura do óxido, tensão de limiar, etc.), tensão de alimentação e temperatura de operação.

A aceitação de um circuito pode ser expressa da seguinte forma:

$$\mathbf{Y}(\mathbf{r}, \mathbf{q}) \in \mathbf{\Phi}. \tag{3.1}$$

O conjunto  $\Phi$  contém a região de especificações aceitáveis no espaço de desempenho do circuito. A região de aceitação  $\Psi$  no espaço de projeto é definida como:

$$Y(r,q) \in \Phi \to r \in \Psi.$$

(3.2)

Um circuito fabricado será considerado aceitável se todos os seus desempenhos reais estiverem dentro dos limites aceitáveis, isto é, se  $S_i^L \leq S_i \leq S_i^U$ , onde os índices L e

3.4. Função Custo 49

*U* correspondem aos limites inferiores e superiores das especificações, respectivamente.

A abordagem proposta para a otimização do desempenho do circuito é um problema de programação não linear e requer a formulação de uma única função custo a ser minimizada, sujeito a um conjunto de restrições de desigualdade, como na seguinte forma padrão:

minimize

$$F_i(\mathbf{r}, \mathbf{q}), i = 1, ..., I$$

sujeito a  $C_j(\mathbf{r}, \mathbf{q}) \le C_{j(ref)}, j = 1, ..., J$  (3.3)

onde I é o número total de  $F_i$  especificações a serem otimizadas e J é o número de  $C_j$  funções de restrições de performance. Aqui, **Y** pode ser reescrita como um conjunto de objetivos de projeto e restrições de performance como **Y**(**r**, **q**) = { $F_1, ..., F_I, C_1, ..., C_I$ }.

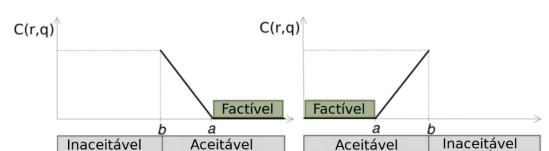

$C_j(\mathbf{r}, \mathbf{q})$  é uma função dependente do tipo de especificação: valor mínimo requerido ( $C_{min}(\mathbf{r}, \mathbf{q})$ ) ou valor máximo requerido ( $C_{max}(\mathbf{r}, \mathbf{q})$ ) (BARROS; GUILHERME; HORTA, 2010). Essas funções são mostradas na figura 16, onde a é o máximo ou mínimo valor requerido e b é o valor limite entre a performance aceitável e inaceitável. Os valores entre os pontos entre a e b retornam valores intermediários para as funções de restrições. Esses valores levam a um custo adicional para a função custo conforma a distância do valor obtido estiver do valor desejado. Caso o valor obtido esteja à esquerda do valor desejado, em um caso de minimização, o custo adicional é zero. De forma análoga, caso o valor obtido esteja à direita do valor desejado, em caso de maximização, o custo atribuído a função custo é zero. Ou seja, as restrições possuem um valor desejado e um intervalo considerado aceitável. O valor atribuído à função custo é calculado de forma linear, conforme mostrado na figura 16.

A função custo utilizada é calculada de acordo com um sistema de penalidades, onde o valor é obtido através de um somatório de penalidades calculadas de acordo com a diferença entre o valor esperado e o valor simulado para cada especificação, como mostra a equação:

$$f_c(\mathbf{r}, \mathbf{q}) = \sum_{i=1}^{I} w_i \cdot \hat{F}_i(\mathbf{r}, \mathbf{q}) + \sum_{i=1}^{J} v_j \cdot \hat{C}_j(\mathbf{r}, \mathbf{q}).$$

(3.4)

Aqui,  $w_i$  e  $v_j$  são pesos que indicam a importância relativa de objetivos e restrições de projeto, respectivamente.  $\hat{F}$  and  $\hat{C}$  são funções de restrições e objetivos de projeto normalizadas, a fim de manter todos os fatores de soma na mesma ordem de grandeza.

O valor calculado para a função custo representa uma figura de mérito para a otimização. Utilizando a estratégia apresentada, uma função custo com valor zero representa um circuito em que todas as especificações foram atingidas.

Como exemplo, consideremos uma especificação, como o ganho (Av0) do ampop, onde o projetista informa à ferramenta que deseja-se atingir 70 dB e que o mínimo

Figura 16 – Métricas de avaliação das restrições de projeto: (a) especificação de valor mínimo exigido e (b) especificação de valor máximo exigido.

Adaptado de Severo e Girardi (2011)

aceitável como uma solução válida é 50 dB. Se o valor obtido na simulação for maior ou igual a 70 dB, será atribuído zero à função custo. Caso contrário, se o valor for menor que 70 e maior ou igual a 50 dB, será atribuído um valor maior que zero e menor que 1. Por exemplo, se ganho for igual a 60 dB, o valor adicionado à função custo será de 0.5 multiplicado pelo peso de importância dado à essa especificação. Ou ainda, caso o valor obtido seja menor que 50 dB, essa solução é considerada fora da região factível e a solução é descartada.

Para uma especificação de otimização é necessário um valor de referência. Por exemplo, considerando a potência como uma especificação de otimização, para que seja possível atribuir um valor à função custo de acordo com a potência medida, é necessário uma referência de grandeza que se deseja atingir. Atribui-se à função custo uma penalidade dada de acordo com a potência medida dividido pela potência de referência multiplicado pelo peso dado à essas especificação. Considerando que deseja-se minimizar a potência e o projetista informa como referência uma valor de 10  $\mu$ W (grandeza que ele considera satisfatória) e na simulação foi obtido um consumo de 20  $\mu$ W, será atribuído à função custo um valor de 2 multiplicado pelo peso dado para essa especificação pelo projetista. Se o valor da simulação obtido foi de 10  $\mu$ W, ainda assim será atribuído o valor de 1 à função custo, o que leva o algoritmo a continuar tentando reduzir essa especificação.

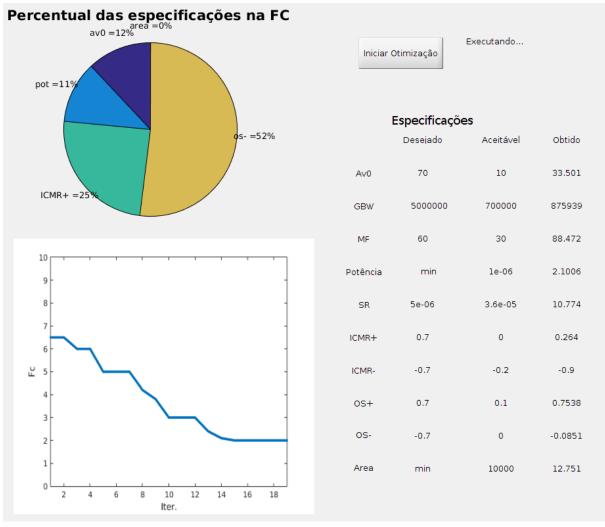

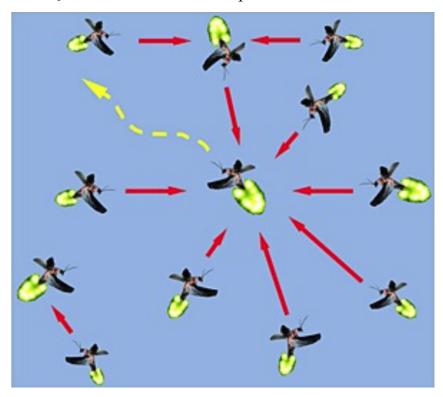

A ferramenta permite também observar, através de uma interface gráfica, quais especificações não estão atingindo o valor desejado e qual o impacto delas no valor da função custo a cada iteração do algoritmo. O gráfico é gerado apenas nos casos em que a solução seja considerada válida, ou seja, aquelas soluções que apresentam todas as especificações dentro do intervalo aceitável. Isso permite ao projetista observar quais especificações estão mais distante do valor desejado para que, se desejável, ele aumente o peso dessa especificação. A evolução da função custo também pode ser observada nessa GUI (*Graphical User Interface*), como pode ser observado na figura 17.