### Marcelo Pereira Magalhães

# Design and Analysis of an Antenna Array System for Communication Using High-Altitude Platforms

Alegrete, RS

### Marcelo Pereira Magalhães

# Design and Analysis of an Antenna Array System for Communication Using High-Altitude Platforms

Master thesis presented to the Graduate Program in Electrical Engineering, major subject Energy Systems, of Universidade Federal do Pampa (UNIPAMPA, RS), as a partial requirement to obtain the degree of Master in Electrical Engineering.

Universidade Federal do Pampa – UNIPAMPA Graduate Program in Electrical Engineering

Advisor: Prof. Dr. Marcos Vinício Thomas Heckler

Alegrete, RS 12.05.2017

# Ficha catalográfica elaborada automaticamente com os dados fornecidos pelo(a) autor(a) através do Módulo de Biblioteca do Sistema GURI (Gestão Unificada de Recursos Institucionais).

M188d Magalhães, Marcelo Pereira

Design and Analysis of an Antenna Array System for Communication Using High-Altitude Platforms / Marcelo Pereira Magalhães.

105 p.

Dissertação(Mestrado) -- Universidade Federal do Pampa, MESTRADO EM ENGENHARIA ELÉTRICA, 2017.

"Orientação: Marcos Vinício Thomas Heckler".

1. Rede de antenas em microfita. 2. Serviços de comunicações móveis. 3. Dupla-banda e dupla-polarização. 4. Circuitos em alta frequência. 5. Simulações eletromagnéticas. I. Título.

### Marcelo Pereira Magalhães

### Design and Analysis of an Antenna Array System for Communication Using High-Altitude Platforms

Master thesis presented to the Graduate Program in Electrical Engineering, major subject Energy Systems, of Universidade Federal do Pampa (UNIPAMPA, RS), as a partial requirement to obtain the degree of Master in Electrical Engineering.

Master thesis presented and approved in Alegrete, RS, May  $12^{th}$  2017:

Prof. Dr. Marcos Vinício Thomas

Heckler Advisor

Prof. Dr. Alessandro Gonçalves

Girardi

**UNIPAMPA**

Prof. Dr. Xisto Lucas Travassos Junior  $$\operatorname{UFSC}$$

Alegrete, RS 12.05.2017

# Acknowledgements

First of all, I thank Prof. Dr. Marcos Vinício Thomas Heckler, for the dedication in supervising, encouraging, understanding and teaching the technical concepts of the study area, which made possible the accomplishment of this work. I also would like to thank the granted opportunities as travel abroad bringing new knowledge and life experience, for advice and the confidence placed in me during all the work.

To my family, especially to my parents Joel and Vânia Magalhães, which are essential for my academic life. To my brothers Guilherme and Vinícius Magalhães, for support, affection, advice, encouragement and for always being willing to help me when necessary.

To the professors and friends of the Universidade Federal do Pampa, to all laboratory and research group (LEMA) colleagues in particular to Cleiton Lucatel and Diego Fumagalli which were essential in the experimental developments, as well as to the German Aerospace Center (DLR) colleagues in particular to Andreas Winterstein and Lukasz Greda, and all who contributed in some way, always being willing to assist when necessary, providing enriching tips that helped in the accomplishment of the work.

To all, thank you very much!

### **Abstract**

This thesis presents the design and analysis of an antenna array system for mobile communication services in a scenario using high altitude platforms (HAPs). For this purpose, a dual-band and dual-polarized microstrip antenna array has been designed, whereby the array should receive the signal in one band and resend it in the other operating band. These requirements have been fulfilled by using a stacked arrangement, whereby each patch has been fed by independent feed lines. Circular polarization was obtained by the use of square patches with truncated corners. Optimizations were needed so as to compensate the effects of mutual coupling on the axial ratio level. To perform the radiation pattern synthesis for the transmission function, an algorithm to calculate the required excitation coefficients was employed to steer the main beam and to control the side lobe level.

Additionally to the array design, the development of the high-frequency (HF) circuitry for the retransmission is described. The design of the transmitter was done using off-the-shelf components, which have been tested individually prior to the final integration into the final layout. During the tests, the need of knowledge of the electromagnetic properties of the printed circuit layout and the active/passive components is crucial for a successful design. In order to accelerate the development of HF circuitry, a procedure to perform electromagnetic simulations of HF printed circuit boards is proposed. Experimental results demonstrated that this procedure yielded accurate engineering predictions.

**Keywords**: microstrip antenna array, mobile communication services, dual-band and dual-polarized antennas, high-frequency circuitry, electromagnetic simulations.

### Resumo

### Projeto e Análise de um Sistema de Rede de Antenas para Comunicação Utilizando Plataformas de Alta Altitude

Este trabalho apresenta o projeto e análise de um sistema de rede de antenas para serviços de comunicações móveis em um cenário empregando plataformas de alta altitude (HAPs). Para este fim, uma rede de antenas de microfita foi projetada para operar em dupla-banda e dupla-polarização, onde a rede deve receber o sinal em uma banda e reenviá-lo em outra. Esses requisitos foram cumpridos usando uma rede de antenas com múltiplas camadas, onde cada patch foi alimentado por linhas de alimentação independentes. A polarização circular foi obtida pelo uso de patches quadrados com os cantos truncados. Foram necessárias otimizações para compensar os efeitos de acoplamento mútuo no nível da razão axial. Para realizar o controle do diagrama de irradiação para o modo de transmissão, utilizou-se um algoritmo para calcular os pesos necessários para apontar o lóbulo principal e controlar o nível dos lóbulos laterais.

Adicionalmente ao projeto da rede, o desenvolvimento de um circuito em alta frequência (HF) para a retransmissão foi descrito. O projeto do circuito transmissor foi realizado empregando componentes comerciais, que foram testados individualmente antes da integração final. Durante os testes em bancada, ficou evidente a necessidade de predição do comportamento eletromagnético do layout da placa de circuito impresso e dos componentes ativos/passivos para obtenção de bons resultados. Com o intuito de acelerar o processo de desenvolvimento de circuitos em HF, um procedimento para a realização de simulações eletromagnéticas de placas de circuito impresso foi proposto. Os resultados experimentais demonstraram que este procedimento produziu bons resultados.

Palavras-chave: rede de antenas em microfita, serviços de comunicações móveis, antenas com dupla-banda e dupla-polarização, circuitos operando em alta frequência, simulações eletromagnéticas.

# List of Figures

| Figure 1 – Typical retrodirective antenna configurations                             | 17 |

|--------------------------------------------------------------------------------------|----|

| Figure $2$ — Different altitude levels for geographic and communication systems      | 18 |

| Figure 3 – Flow chart of a retrodirective system                                     | 19 |

| Figure $4$ – Linear array with approximation valid for the far-field region          | 20 |

| Figure 5 – Structure of an retrodirective antenna, cross-section view                | 21 |

| Figure 6 – Retrodirective antenna array structure, isometric view                    | 22 |

| Figure 7 – Designed retrodirective antenna array, in different views                 | 23 |

| Figure 8 $-$ Reflection coefficient for the dual-band antenna array                  | 24 |

| Figure 9 – Axial ratio for the dual-band antenna array                               | 24 |

| Figure $10$ – Radiation pattern for the dual-band antenna array                      | 24 |

| Figure 11 $-$ Normalized radiation pattern at 5.8 GHz without optimization           | 26 |

| Figure $12$ – Normalized electric field for the MATLAB code and HFSS solution        | 27 |

| Figure 13 – Normalized electric field for discrete and ideal control                 | 28 |

| Figure $14$ – Normalized radiation pattern for ideal and discrete control, in dBi    | 29 |

| Figure $15$ – Width of the main lobe as a function of the beamsteering               | 30 |

| Figure 16 – Analysis for beamsteering to $-30^\circ$ for a fully functional array    | 31 |

| Figure 17 – Optimized patterns for different beamsteering angles                     | 32 |

| Figure 18 – Analysis for beamsteering to $-30^\circ$ with loss of one Rx-element     | 33 |

| Figure 19 – Analysis for beamsteering to $-30^\circ$ with loss of two Rx-elements    | 33 |

| Figure 20 – Optimization for different beamsteering angles and failure of element 1. | 34 |

| Figure 21 – Optimization for different beamsteering angles and failure of element 4. | 35 |

| Figure 22 – Prototyped antenna array layers                                          | 36 |

| Figure 23 – Prototype prior to and after glueing                                     | 36 |

| Figure 24 – Soldered vias for lower frequency patches                                | 37 |

| Figure 25 – Prototyped final structure for the retrodirective antenna array          | 37 |

| Figure 26 – Measured reflection coefficient for both frequencies                     | 38 |

| Figure 27 – Measured radiation pattern for both frequencies                          | 38 |

| Figure 28 – Initial architecture for the Tx-circuitry                                | 39 |

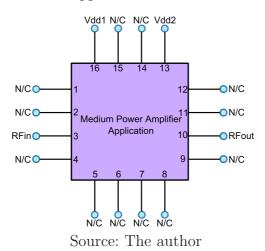

| Figure 29 – Electric circuit for the medium power amplifier ERA-1SM+                 | 40 |

| Figure 30 $-$ Designed schematic for the MPA ERA-1SM+, first prototype               | 41 |

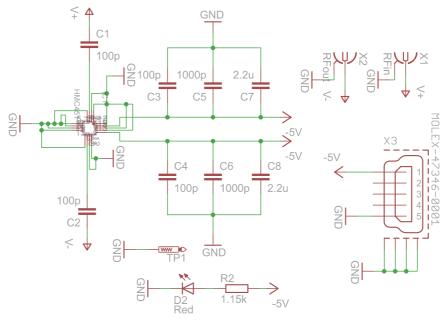

| Figure 31 – Layout designed for the MPA ERA-1SM+, first prototype                    | 41 |

| Figure 32 – Schematic designed for the MPA ERA-1SM+, second prototype                | 42 |

| Figure 33 $-$ Layout designed for the MPA ERA-1SM+, second prototype                 | 42 |

| Figure 34 $-$ Electromagnetic model of the PCB for the MPA1, first prototype         | 42 |

| Figure 35 – Schematic circuit for the MPA ERA-1SM+, first prototype                  | 43 |

| Figure 36 – Simulated and measured results for the PCBs, first prototype             | 43 |

| Figure 37 – Measured results for both prototypes of MPA ERA-1SM+                        | 44 |

|-----------------------------------------------------------------------------------------|----|

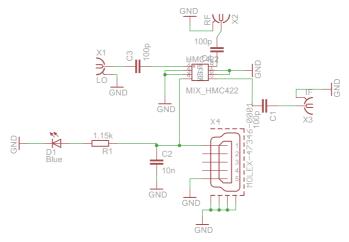

| Figure 38 – Device connections for the MIXER1 stage, first prototype                    | 45 |

| Figure 39 – Schematic designed for the MIXER1 stage, first prototype                    | 45 |

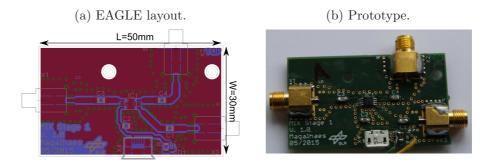

| Figure 40 $-$ Layout designed for the MIXER1 stage, first prototype                     | 45 |

| Figure 41 – Device connections for the MIXER1 stage, second prototype                   | 46 |

| Figure $42$ – Schematic designed for the MIXER1 stage, second prototype                 | 46 |

| Figure 43 – Layout designed for the MIXER1 stage, second prototype                      | 46 |

| Figure $44$ – Schematic designed for the MIXER1 stage, second prototype                 | 47 |

| Figure $45$ – Layout designed for the MIXER1 stage with filtering, second prototype.    | 47 |

| Figure 46 – Measurement results for the MIXER1 stage                                    | 48 |

| Figure 47 – Different techniques to merge LC circuits in LPF designs                    | 49 |

| Figure 48 – Adopted structure for the LPF design                                        | 50 |

| Figure 49 $-$ Defined electrical circuit for the LPF operating at 1.9 GHz. $$           | 51 |

| Figure 50 – Microstrip lines equivalent to lumped components                            | 51 |

| Figure 51 $-$ Width and length estimation using Txline for the LPF at 2.35 GHz          | 52 |

| Figure 52 – Designed LPF using FR4 material                                             | 53 |

| Figure 53 – Probe station to measurements of PCBs                                       | 53 |

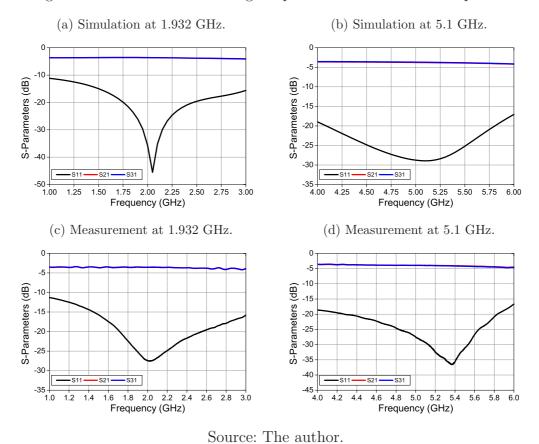

| Figure 54 – S-parameters for the LPF operating at 1.9 GHz                               | 54 |

| Figure 55 – Recommended application circuit for the variable gain amplifier             | 55 |

| Figure 56 – Schematic designed for the VGA                                              | 55 |

| Figure 57 – Layout designed for the VGA, top view                                       | 56 |

| Figure 58 – Simulated PCB for the variable gain amplifier                               | 56 |

| Figure 59 – Designed circuit for the VGA                                                | 57 |

| Figure 60 – Simulated results for the variable gain amplifier                           | 57 |

| Figure 61 $-$ Measured results for two prototypes of the VGA using serial control. $$ . | 58 |

| Figure 62 – Recommended application circuit for the phase shifter                       | 59 |

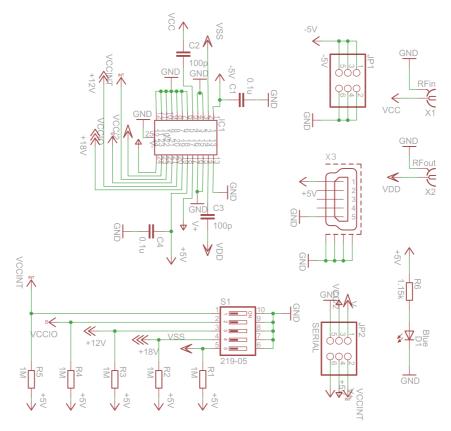

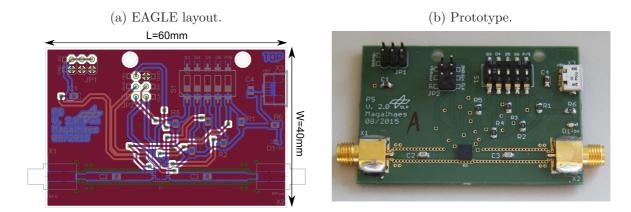

| Figure 63 – Schematic designed for the phase shifter, first prototype                   | 60 |

| Figure 64 – Layout designed for the phase shifter, first prototype                      | 60 |

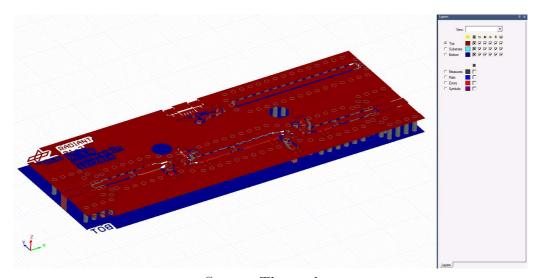

| Figure 65 – Schematic designed for the phase shifter, second prototype                  | 61 |

| Figure 66 – Layout designed for the phase shifter, second prototype                     | 61 |

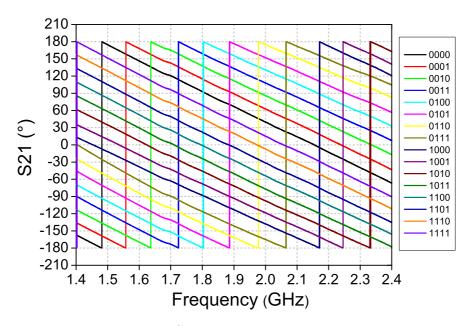

| Figure 67 $-$ Measured phase of the S21-parameter for the digitally controlled PS. $$ . | 62 |

| Figure 68 – Schematic designed for the MIXER2 stage                                     | 63 |

| Figure 69 – Layout designed for the MIXER2 stage, first prototype                       | 63 |

| Figure 70 – Layout designed for the MIXER2 stage, second prototype                      | 64 |

| Figure 71 – Measurement results for the MIXER2 stage                                    | 64 |

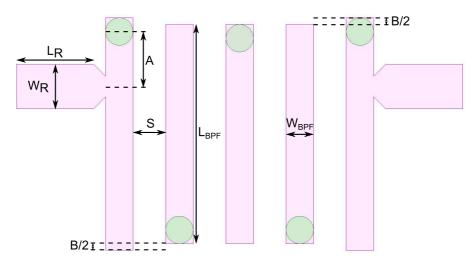

| Figure 72 – Adopted structure for the band-pass filter design                           | 65 |

| Figure 73 – Interdigital distributed BPF model                                          | 66 |

| Figure 74 – Designed BPF operating at 7.0 GHz                                           | 68 |

| Figure 75 – Obtained S-parameters for the BPF operating at 7 GHz                        | 68 |

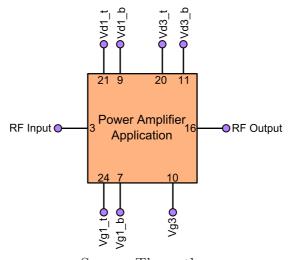

| Figure 76 – Recommended application circuit for the PA                            | 69 |

|-----------------------------------------------------------------------------------|----|

| Figure 77 – Schematic designed for the power amplifier                            | 70 |

| Figure 78 – Layout designed for the power amplifier                               | 70 |

| Figure 79 – Recommended circuit for the MPA2 from Hittite                         | 71 |

| Figure 80 – Schematic designed for the MPA2 from Hittite                          | 71 |

| Figure 81 – Layout designed for the MPA2 model 1                                  | 72 |

| Figure $82$ – Schematic designed for the second stage of MPA from Mini-circuits   | 72 |

| Figure 83 – Layout designed for the MPA2 model 2                                  | 72 |

| Figure 84 – Designed PCB for the power amplifier                                  | 73 |

| Figure 85 – Designed circuit for the power amplifier                              | 73 |

| Figure 86 – Simulated S-parameters for the power amplifier                        | 74 |

| Figure 87 – Measured S-parameters for the MPA2                                    | 74 |

| Figure 88 – Comparison between MPAs ERA-1SM+ and GALI-2+                          | 75 |

| Figure 89 – New architecture for the Tx-circuitry without VGA                     | 75 |

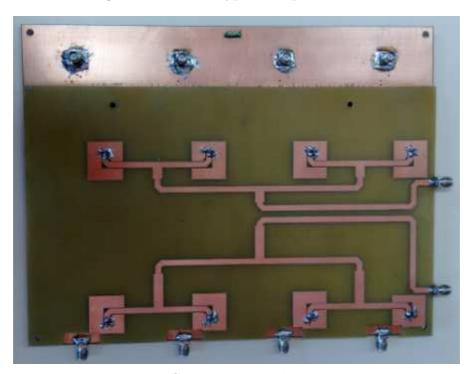

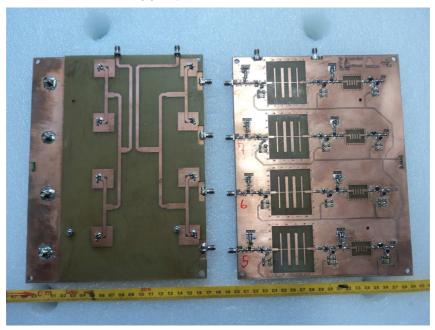

| Figure 90 – Design boards for integration of the Tx-channel                       | 76 |

| Figure 91 – Assembled PCBs for the Tx-circuitry                                   | 76 |

| Figure 92 – Measured results for the PCB1                                         | 77 |

| Figure 93 – Measured results for the PCB2 and PCB3                                | 78 |

| Figure 94 – Complete Tx-channel.                                                  | 78 |

| Figure 95 – Measured results for the complete channel                             | 79 |

| Figure 96 – Final architecture without phase shifters                             | 79 |

| Figure 97 – Measured S-parameters for the complete channel without phase shifter. | 80 |

| Figure 98 – Electromagnetic models of the power dividers for both LO frequencies. | 80 |

| Figure 99 – Results for the designed power dividers in both frequencies           | 81 |

| Figure 100-Prototyped 1x4 power divider                                           | 81 |

| Figure 101–Prototyped boards with power dividers                                  | 82 |

| Figure 102 – Measured spectrum for the 1x8 channels                               | 83 |

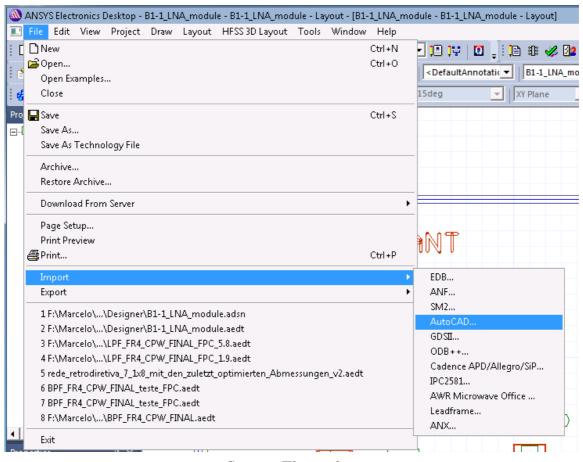

| Figure 103–Importing DXF files                                                    | 85 |

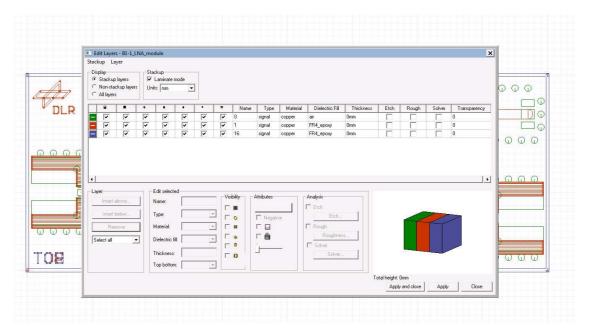

| Figure 104 – Verification of the PCB layers                                       | 86 |

| Figure 105 – Selection of the relevant layers.                                    | 86 |

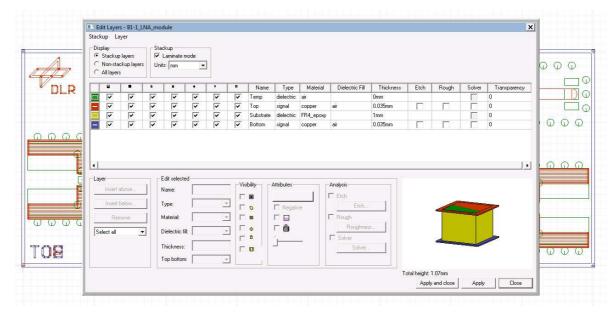

| Figure 106 – Details of the PCB stack-up                                          | 87 |

| Figure 107-Allocation of the vias in the PCB                                      | 88 |

| Figure 108–PCB with the final layers, isometric view                              | 88 |

| Figure 109—Creating ports in the PCB, top view                                    | 89 |

| Figure 110-Setting up the HFSS extents                                            | 89 |

| Figure 111 – Dialog box to set up an HFSS solution                                | 90 |

| Figure 112—Including an HFSS frequency sweep                                      | 90 |

| Figure 113—Circuit design using the PCB as an N-port model                        | 91 |

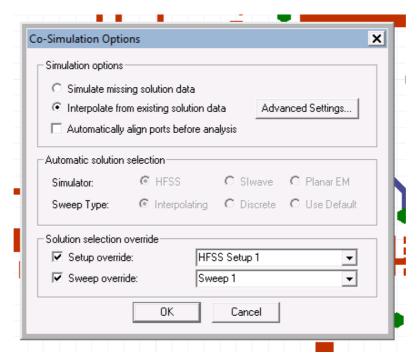

| Figure 114 – Setting up a co-simulation                                           | 92 |

|                                                                                   |    |

| Figure 115—Setting up the Designer setup                                         | 92 |

|----------------------------------------------------------------------------------|----|

| Figure $116-S$ -parameters as a function of the frequency for the PCB simulation | 93 |

| Figure 117–Flow chart of the script steps                                        | 94 |

| Figure 118—Comparison and validation of the Designer script                      | 96 |

# List of Tables

| Table 1 – Th  | nicknesses of the antenna layers                                  | 21 |

|---------------|-------------------------------------------------------------------|----|

| Table 2 – Ini | itial dimensions for the antenna array simulation                 | 22 |

| Table 3 – Fir | nal dimensions for the antenna array simulation                   | 25 |

| Table 4 - Ma  | agnitude and phase of the calculated currents using the PSO       | 26 |

| Table 5 – Ide | eal and discrete current magnitudes for the cases of steering     | 28 |

| Table 6 - Co  | prrection factor for different number of sections                 | 50 |

| Table 7 – Fir | nal dimensions for the LPF design in CPW technology at 1.9 GHz    | 54 |

| Table 8 – Tru | uth table for 4-bit digital phase shifter                         | 59 |

| Table 9 – Fir | nal dimensions for the BPF designed in CPW technology at 7.0 GHz. | 69 |

| Table 10 – Me | easured values for each complete channel                          | 83 |

# Content

| 1       | INTRODUCTION                                                | 10 |

|---------|-------------------------------------------------------------|----|

| 2       | DUAL-BAND AND DUAL-POLARIZED ANTENNA                        | 20 |

| 2.1     | Design Specifications                                       | 20 |

| 2.2     | Simulation Results                                          | 22 |

| 2.3     | Parametric Study of the Antenna Array                       | 25 |

| 2.3.1   | Impact of the RF components resolution                      | 25 |

| 2.3.2   | Failure of one or more elements                             | 30 |

| 2.3.2.1 | Fully functional array                                      | 31 |

| 2.3.2.2 | Array with faulty element in the receiver                   | 32 |

| 2.3.2.3 | Array with faulty element in the transmitter                | 34 |

| 2.4     | Antenna Array Prototype Measured and Results                | 35 |

| 3       | RF FRONT-END CIRCUITS                                       | 39 |

| 3.1     | Design of the Individual Components                         | 40 |

| 3.1.1   | Medium power amplifier - first stage                        | 40 |

| 3.1.1.1 | First prototype                                             | 40 |

| 3.1.1.2 | Second prototype                                            | 41 |

| 3.1.1.3 | Measurement and simulation results                          | 42 |

| 3.1.2   | Mixer - first stage                                         | 44 |

| 3.1.2.1 | First prototype                                             | 45 |

| 3.1.2.2 | Second prototype                                            | 46 |

| 3.1.2.3 | Measurement results                                         | 47 |

| 3.1.3   | Low-pass filter operating at 1.9 GHz                        | 48 |

| 3.1.3.1 | Calculation of the initial parameters                       | 50 |

| 3.1.3.2 | Definition of the electrical circuit                        | 51 |

| 3.1.3.3 | Convertion of the components to equivalent microstrip lines | 51 |

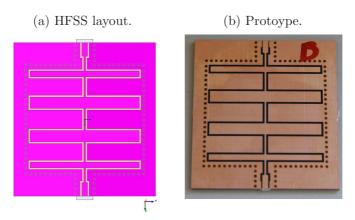

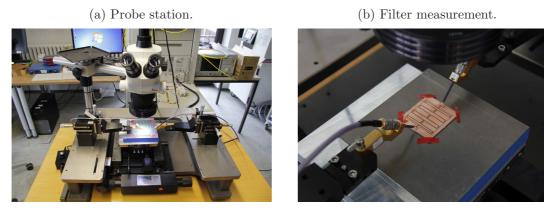

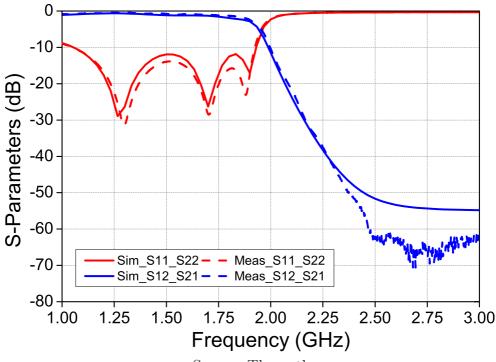

| 3.1.3.4 | Simulation of LPF using HFSS software                       | 53 |

| 3.1.3.5 | Measurement and simulation results                          | 53 |

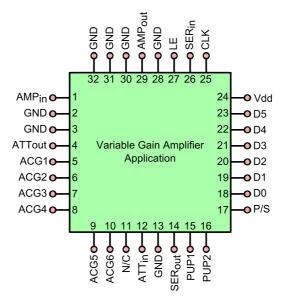

| 3.1.4   | Variable gain amplifier                                     | 54 |

| 3.1.4.1 | Measurement and simulation results                          | 56 |

| 3.1.5   | Phase shifter                                               | 58 |

| 3.1.5.1 | First prototype                                             | 60 |

| 3.1.5.2 | Second prototype                                            | 61 |

| 3.1.5.3 | Measurement results                                         | 62 |

| 3.1.6   | Mixer - second stage                                        | 62 |

| 3.1.6.1 | First prototype                                            |  |

|---------|------------------------------------------------------------|--|

| 3.1.6.2 | Second prototype                                           |  |

| 3.1.6.3 | Measurement results                                        |  |

| 3.1.7   | Band-pass filter operating at 7.0 GHz                      |  |

| 3.1.7.1 | Calculation of the initial parameters                      |  |

| 3.1.7.2 | Simulation of BPF using HFSS software                      |  |

| 3.1.7.3 | Measurement and simulation results                         |  |

| 3.1.8   | Medium power amplifier - second stage                      |  |

| 3.1.8.1 | Design of the power amplifier                              |  |

| 3.1.8.2 | Design of the MPA2 stage                                   |  |

| 3.1.8.3 | Measurement and simulation results                         |  |

| 3.2     | Integration of the Individual Components                   |  |

| 3.3     | Integration of the Complete Channel                        |  |

| 3.4     | Integration of the Eight Channels                          |  |

|         |                                                            |  |

| 4       | PCB SIMULATIONS                                            |  |

| 4.1     | Procedure for Accurate Simulation of PCBs Working at HF 84 |  |

| 4.1.1   | Importing the DXF file                                     |  |

| 4.1.2   | Verification of the most relevant layers                   |  |

| 4.1.3   | Setting up the PCB stack-up                                |  |

| 4.1.4   | Recreating the vias from the original PCB                  |  |

| 4.1.5   | Setting up the ports and HFSS extents                      |  |

| 4.1.6   | HFSS setup                                                 |  |

| 4.1.7   | Creating a Circuit Design                                  |  |

| 4.1.8   | Simulation of the model                                    |  |

| 4.2     | Script to Include Vias Automatically on PCBs               |  |

| 4.2.1   | Designer script template                                   |  |

| 4.2.2   | Setup of the input parameters                              |  |

| 4.2.3   | Import and setup of via diameters                          |  |

| 4.2.4   | Import and setup of via coordinates                        |  |

| 4.2.5   | Creation of a Ansys Designer script output                 |  |

| 4.2.6   | Validation of the script                                   |  |

| 5       | CONCLUSION                                                 |  |

|         | APPENDIX A – DESIGNER TEMPLATE                             |  |

|         | APPENDIX B – MATLAB CODE FOR VIAS IMPORTING 99             |  |

|         | REFERENCES                                                 |  |

### 1 Introduction

Adaptive antenna systems have been widely used in recent years and have become an alternative for applications that require efficiency and high quality of signal, such as in mobile communications systems and aerospace applications (CHANDRAN, 2004). This type of antenna has become attractive due to the possibility of performing the beamsteering of the main lobe in the desired direction and suppressing the side lobes simultaneously only by means of electronic control of the excitation of each antenna, thus avoiding the need to mechanically steer the antenna to point its main beam in the desired direction. This feature prompted a growing development of beamforming and beamshaping techniques, in order to allow the implementation of adaptive antennas (CHANDRAN, 2004).

Fully adaptive antennas demand the use of an algorithm to estimate the direction of arrival and another for shaping the radiation pattern. Pattern synthesis may be challenging especially for applications where the system must have a fast update rate. For the particular case of data relay systems, this problem can be overcome by the use of retrodirective arrays, which are a particular class of adaptive antennas that is able to retransmit the received signal without any signal processing to estimate the direction of arrival. This is achieved by means of phase conjugation of the signals received by the array elements (MAGALHAES et al., 2015). The classical example of retrodirective antennas is the Van Atta configuration, which is a passive array where the phase conjugation is obtained simply by interconnecting the array elements directly through lines with the same electrical length (MIYAMOTO; ITOH, 2002). However, for long-distance communications where large free space losses are present, the use of active devices cannot be avoided. Moreover, the Van Atta array does not allow frequency translation, which may be required if the array is to be installed on a sattelite or on a high altitude platform (HAP), whereby uplink and downlink frequencies are normally different. Fig. 1 depicts the Van Atta and an active reflectarray topologies.

The synthesis of antennas and arrays based on optimization algorithms such as PSO has been reported in some recent studies. In (REN; CHANG, 2006), the design of a planar array of retrodirective antennas operating at 5.8 GHz for wireless application is presented, while (HOOD; TOPSAKAL, 2007) discusses the implementation of PSO in MATLAB to design a microstrip antenna operating with dual-band behaviour. Also, in (PAPADOPOULOS et al., 2006) and (ZUNIGA; ERDOGAN; ARSLAN, 2010), PSO has been used to synthesize radiation patterns. The development of some architectures of retrodirective antennas for different scenarios of communication is presented in (GOSHI; ITOH, 2008). An interesting approach is reported in (HSU et al., 2010) using adaptive antennas in order to synthesize the radiation pattern through PSO algorithm. In

(a) Van Atta array. (b) Active array. A∠0°  $A \angle \delta$  $A\angle 2\delta$  $A \angle \delta$ AZ0°  $A \angle 3\delta$  $A\angle 2\delta$  $A \angle 3\delta$  $A \angle 3\delta$  $A\angle 2\delta$ A∠0°  $A \angle \delta$  $A \angle \delta$  $A \angle 3\delta$  $A\angle 2\delta$ A∠0° Antenna Antenna Antenna Antenna Antenna Antenna Array symmetry Transmission lines with the same electric length

Figure 1 – Typical retrodirective antenna configurations.

(ANDRE; LEONARD, 1964), the study of an retrodirective system and RF circuit considering element failures are presented, while (MIYAMOTO et al., 2003) and (CHEN; YAN, 2009) present the design of a smart antenna/retrodirective array applied to wireless sensor systems. The approach of a 60 GHz retrodirective array system with an efficient power management of the LO for wireless multimedia sensor server applications is presented in (LIM; ITOH, 2008). In (KAWAZOE et al., 2005) and (OKAZAKI et al., 2007), the design of a reconfigurable RF circuit architecture for dynamic power reduction and future band-free mobile terminals are presented, respectively.

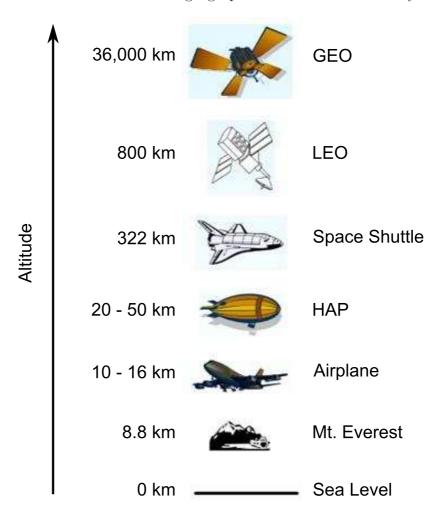

Retrodirective systems used on HAPs or sattelites can be employed in several applications, such as: replacing communication base stations when they are broken, transponders to relay a signal back to the interrogator, collision avoidance systems, disaster scenarios, and also in regional television systems (BISCHL, 2008). An alternative approach using retrodirective antennas on HAPs could replace most of the current available ground infrastructure (VHF/UHF repeaters) for broadcasting. As it can be observed in Fig. 2, high altitude plataforms work at altitudes between 20 km and 50 km from the Earth surface, while other systems work at higher altitudes such as geostacionary-earth orbit (GEO) and low-earth orbit (LEO) satellites (PARK, 2008). For this reason, HAPs tend to be more cost effective than satellite-based communications. Another advantage is the possibility to do maintenance periodically.

The particle swarm optimization (PSO) algorithm has been used to calculate the excitations of each antenna. The PSO was chosen due to the advantages compared to other techniques. In (SCHLOSSER; TOLFO; HECKLER, 2015), the PSO has been applied to radiation pattern synthesis with faster convergence in comparison to the genetic

Figure 2 – Different altitude levels for geographic and communication systems examples.

Source: Adapted from (PEREIRA, 2015).

algorithm (GA). PSO is an evolutionary technique inspired in the social behaviour of birds (KENNEDY; EBERHART, 1995). The name "swarm" comes from the irregular movement of the particles in the computational domain (CARTWRIGHT, 2002). The PSO is based on studies in artificial life and social psychology, as well as in engineering and computer science. It utilizes a population of individuals, referred to as particles, that fly in a hyperspace with variable speed. In each iteration, the speed and position of each particle are adjusted by taking into account the best overall historical position and their relative distance to the particle that is assumed to be closest to the optimum solution (best place). By doing so, each particle evolves naturally to the optimum or to a near-optimum solution (CARTWRIGHT, 2002).

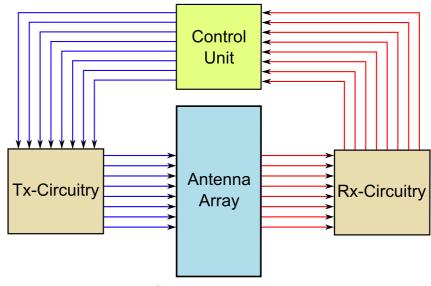

The defined antenna array for the present study is composed of circularly polarized microstrip antennas, designed to operate in dual-band and with dual-polarization. These features are suitable for installation on HAPs, which is one the main goals of the proposed design. The retrodirective system works basically with the antenna array receiving the

signal at 5.8 GHz and transmitting at 7.0 GHz. The received signal should be processed by a control unit. Algorithms such as PSO or Taguchi (WENG; YANG; ELSHERBENI, 2007) can be used in order to perform the beamforming of the radiation pattern for the retransmission. Thus, with the calculated excitations, the signal is processed using a Tx-circuit that provides each array element with the required magnitude and phase. Fig. 3 presents a flow chart showing the steps described previously. The main focus of this work are the investigation of the antenna array properties and of the needed Tx-circuitry. The optimization with PSO is carried out with the active patterns of the array elements, which have been computed using the electromagnetic simulator Ansys HFSS (ANSYS Corp., 2013). The Tx-circuitry is composed of 8 channels that perform the frequency translation from the control unit outputs (31 MHz) to the antenna array (7.0 GHz). This work was developed at UNIPAMPA and partially at the German Aerospace Center (DLR), in Germany. The scientific contributions of this work are the design of an antenna array that operates with dual-band and dual-polarization, and the procedure to accelerate the design of printed circuit boards operating at microwave frequencies.

Figure 3 – Flow chart of a retrodirective system.

Source: The author.

The work is divided into the following chapters: Chapter 2 presents the design of a dual-band and dual-polarized antenna array suitable for retrodirective systems. Chapter 3 discusses the development and measurements of the designed RF circuitry for the retransmitting function. Chapter 4 presents a procedure explaining how to simulate high frequency (HF) printed circuit boards using ANSYS Designer and ANSYS HFSS software. Finally, in Chapter 5 the concluding remarks are described.

## 2 Dual-Band and Dual-Polarized Antenna

### 2.1 Design Specifications

Antenna arrays are widely used due to advantages such as the possibility to shape the radiation pattern, increasing the directivity and higher flexibility in the design, which are characteristics that are not possible by using standalone antennas. The special class of retrodirective microstrip arrays exhibit the feature to retransmit a signal back to the direction of arrival. Among several other applications, the target investigated in this work is a retrodirective array for high altitude platforms, which are allowed to operate at 5.8 GHz for the uplink (receiving mode) and at 7.0 GHz for the downlink (transmitting mode). In order to increase isolation between the uplink and downlink channels, the array shall operate with right-hand circular polarization (RHCP) in the receiving mode and with left-hand circular polarization (LHCP) to transmit the signal back. The bandwidth has been specified to be 100 MHz for the antenna array and 50 MHz for the RF circuits.

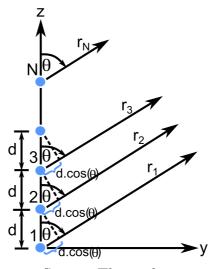

Figure 4 – Linear array with approximation valid for the far-field region.

Source: The author.

Considering the radiation pattern of only one element, it is not possible to perform the beamforming or beamsteering. For long distance communications the required gain must be high, and an antena array structure is necessary. Antenna arrays can be composed of linear or planar structures. A linear arrangement is shown in Fig. 4 for the case of N antennas. The total electric field is calculated by the vector sum of the electric fields radiated by each element. Therefore, it is necessary that the fields interfere constructively in the desired direction  $\theta_p$ . The parameters to realize the radiation pattern control are: number of elements, antenna array geometric distribution, magnitude and phase of each

element excitation, distance between the elements and the electric field that is particular for each single element (BALANIS, 2012).

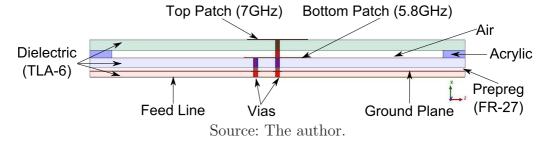

In order to fulfill the specifications above, the array element has been designed with two stacked corners-truncated patches (POZAR, 1992; PEREIRA; HECKLER, 2015). In order to improve isolation between the receiving (Rx) and transmitting (Tx) channels, each patch has been fed by independent microstrip lines, which are connected to the respective patch by means of conducting vias. Fig. 5 presents the antenna geometry, where the dielectric layers are composed of two layers of the laminate Taconic TLA-6 (Taconic Corp., 2008) with thicknesses of 1.96 mm (top and middle layers) and 1.02 mm (bottom layer). This material was chosen due to its low losses, low and stable dielectric constant  $\varepsilon_r = 2.62$ , and good mechanical and thermal properties, which are interesting features for the antennas to be installed on HAPs. The bottom and the middle layers were glued using FastRise-FR27 (Taconic, 2013), which is a prepreg with thickness of 0.107 mm and dielectric constant of  $\varepsilon_r = 2.75$ . Two of FR27 layers have been used in this implementation. In order to achieve the desired bandwidth, an 1.4 mm thick air layer has been inserted between the stacked patches. The thicknesses of all layers are summarized in Table 1.

Figure 5 – Structure of an retrodirective antenna, cross-section view.

Table 1 – Thicknesses of the antenna layers.

| Layer              | Thickness (mm) |

|--------------------|----------------|

| Top Patch          | 0.035          |

| Top TLA-6 Layer    | 1.960          |

| Air                | 1.400          |

| Bottom Patch       | 0.035          |

| Middle TLA-6 Layer | 1.960          |

| Glue (Prepreg) 2   | 0.107          |

| Glue (Prepreg) 1   | 0.107          |

| Ground Plane       | 0.035          |

| Bottom TLA-6 Layer | 1.020          |

| Feed Line          | 0.035          |

#### 2.2 Simulation Results

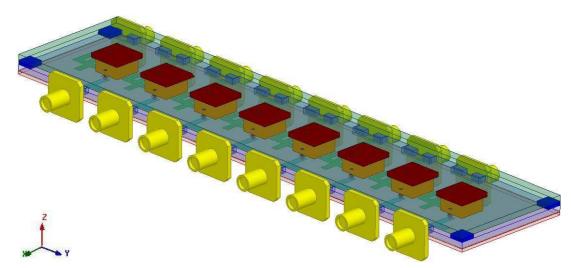

An adaptive antenna array system basically works by controlling the amplitude and phase of each antenna. The first step of optimization consists in simulating the antenna array considering uniform distribution of power for each antenna, by setting the same amplitude and phase at the inputs of each element. In order to compute the embedded patterns of each radiator, the 1x8 antenna array structure shown in Fig. 6 has been simulated in Ansys HFSS. The 8 elements were defined due to the compromise between the array dimensions and the possibility to perform the radiation pattern beamsteering up to  $45\,^{\circ}$  from the boresight direction. The use of few elements allows only the steering in a small angular range, whilst more elements would require a lot of Tx-channels, increasing the project complexity and costs.

Figure 6 – Retrodirective antenna array structure, isometric view.

Source: The author.

Table 2 – Initial dimensions for the antenna array simulation.

| Parameter                                                         | Initial Dimension (mm)                      |

|-------------------------------------------------------------------|---------------------------------------------|

| L Bottom Patch A Bottom Patch L Top Patch A Top Patch W Feed Line | 15.115<br>5.634<br>13.744<br>1.453<br>2.350 |

As it can be observed in Fig. 7, a spacing between the center of each element and the edges of  $d = \lambda/2$  was used, where  $\lambda$  is the wavelength in free space at 7.0 GHz. This results in d = 2.143 cm. The array exhibits total length of L = 19.286 cm and total width of W = 4.286 cm. To perform the antenna excitation, vias with radius of r = 0.5 mm were used. To decrease the losses due to coupling between the Rx and the Tx channels, two kinds of stubs were used. Finally, to obtain the circular polarization, it is necessary to use the technique of corners-truncated patches, where the axial ratio can be controlled by the parameters (cuts)  $A_{Bot}$  and  $A_{Top}$ . The initial parameters for this design were defined from the optimized single antenna in (PEREIRA, 2015) with the dimensions listed in Table 2.

Figure 7 – Designed retrodirective antenna array, in different views.

(a) Spacing between elements and edges, top view. <u>λ/</u>2 <u>λ/</u>2 λ/2  $\lambda/2$ λ/2  $\lambda/2$ λ/2 λ/2 λ/2 λ/2 λ/2 (b) Feed lines schematic, bottom view. Feed Line Decoupling Stub Matching Stub **Bottom Patch Bottom Patch Bottom Patch ABot** Decoupling Line Feed Line Matching Line Top Patch Top Patch Top Patch

Source: The author.

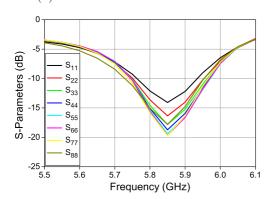

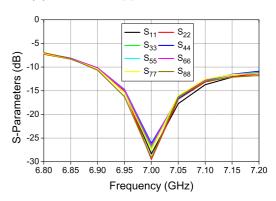

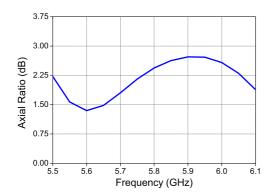

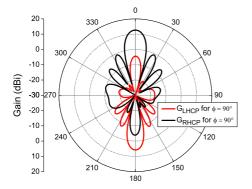

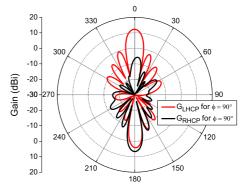

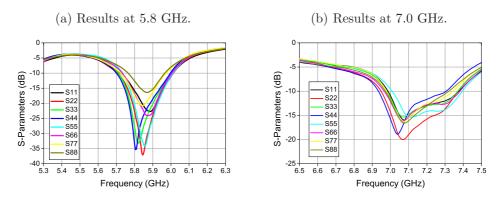

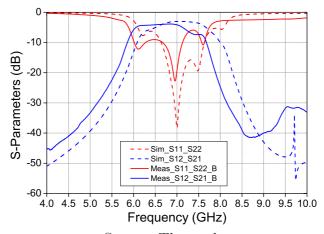

Due to the large simulation time, the analysis for each frequency range was made separately. Firstly, the optimization for the lower band at 5.8 GHz (receiving mode) was performed. Since the radiated fields can affect the receiving channels, all the ports were excited with magnitude A=1 and phase  $\theta=0$ °. After some optimizations, results in terms of S-parameters, axial ratio and radiation pattern are shown in Figs. 8 - 10. One can observe that good results were obtained in terms of impedance matching and axial ratio in the required specifications. The radiation pattern at 5.8 GHz presents gain of 13.0 dBi and large cross-polarization decoupling has been achieved.

Figure 8 – Reflection coefficient as a function of the frequency for the dual-band antenna array.

(a) Results at lower band - 5.8 GHz.

(b) Results at upper band - 7.0 GHz.

Source: The author.

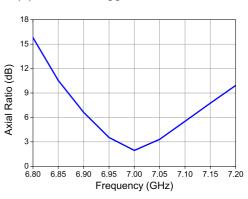

Figure 9 – Axial ratio as a function of the frequency for the dual-band antenna array.

(a) Results at lower band - 5.8 GHz.

(b) Results at upper band - 7.0 GHz.

Source: The author.

Figure 10 – Radiation pattern for the dual-band antenna array.

(a) Results at lower band - 5.8 GHz.

(b) Results at upper band - 7.0 GHz.

The second step consisted in an analysis at the upper frequency range at 7.0 GHz (transmitting mode). Differently than for the previous step, the receiving antennas do not affect the radiation pattern at the transmission mode. Therefore, the ports for the Rx channels were disabled (magnitude A=0 and phase  $\theta=0^{\circ}$ ). At the transmission ports, A=1 and  $\theta=0^{\circ}$  was set. Good results based on the specifications were obtained in terms of impedance matching and axial ratio in the required bandwidth. The radiation pattern at 7.0 GHz presents maximum gain of 13.0 dBi. By optimizing the array at 7.0 GHz, the antenna became slightly detuned at 5.8 GHz, due to the mutual coupling between antennas and axial ratio deterioration. For this reason, the procedure described above had to be carried out repeatedly until acceptable performance has been obtained. The optimized dimensions are listed in Table 3.

Table 3 – Final dimensions for the antenna array simulation.

| Parameter      | Final Dimension |

|----------------|-----------------|

| L Bottom Patch | 15.270          |

| A Bottom Patch | 5.689           |

| L Top Patch    | 13.771          |

| A Top Patch    | 0.938           |

| W Feed Line    | 2.350           |

Source: The author.

### 2.3 Parametric Study of the Antenna Array

### 2.3.1 Impact of the RF components resolution

In any practical communication system, active components are needed in the frontend chain in order to allow the signal to be received or transmitted and then demodulated. In adaptive antennas, beamforming may be obtained in the digital or in the analog domain (MAGALHÃES et al., 2015). In the second case, the magnitudes of the signals received by each antenna may be controlled by introducing a variable gain amplifier (VGA) in the Rx chain of each array element. In the present study, simulations were carried out to assess the performance of the array in receiving mode. The radiation pattern of the array at 5.8 GHz with uniform current distribution and steering to the boresight is shown in Fig. 11, where the calculated radiation pattern and coded in MATLAB fits the results obtained directly with HFSS. This pattern is not optimized and, therefore, the level of the first side lobe is around 13 dB below the main beam.

Figure 11 – Normalized radiation pattern of the retrodirective antenna array at 5.8 GHz without optimization, in dB.

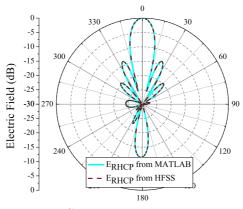

By using PSO, the pattern can be optimized by reducing the side lobe level. To demonstrate the technique, radiation patterns were synthesized for the cases of steering the main beam to 0°, 15° and 30° from the array boresight ( $\theta=0$ °) and by setting SLL=-20 dB. The patterns generated after the optimization of the currents and calculated by the developed tool in MATLAB are shown in Fig. 12, where one can see that the levels of the side lobes satisfied the requirements (MAGALHÃES et al., 2015). The currents calculated by PSO for these three cases are presented in Table 4. It should be pointed out that the angular range considered for the optimization is lonely the upper hemisphere. The lobe in the lower part of the pattern (90°  $\leq \theta \leq$  180°) is a result of back radiation that cannot be suppressed by array synthesis techniques, since it is an intrinsic property of the designed array elements. For validation purposes, the calculated currents have been introduced in the HFSS model, with the resulting pattern shown in dotted lines in Fig. 12. Excellent agreement between the results provided with the MATLAB code and those from HFSS can be verified.

Table 4 – Magnitude and phase of the calculated currents using the PSO algorithm for different cases of beamsteering.

| Element | Steering of 0° |       | Steering of 15° |                  | Steering of 30° |                  |

|---------|----------------|-------|-----------------|------------------|-----------------|------------------|

| Diement | Mag.           | Phase | Mag.            | Phase            | Mag.            | Phase            |

| 1       | 0.793          | 0 °   | 0.462           | 0 °              | 0.177           | 0 °              |

| 2       | 0.507          | 0 °   | 0.363           | −38.60°          | 0.211           | $-76.82^{\circ}$ |

| 3       | 0.862          | 0 °   | 0.842           | −77.20°          | 0.773           | $-153.6^{\circ}$ |

| 4       | 1.000          | 0 °   | 1.000           | −115.8°          | 1.000           | $-230.4^{\circ}$ |

| 5       | 0.966          | 0 °   | 0.936           | $-154.4^{\circ}$ | 0.771           | $-307.3^{\circ}$ |

| 6       | 0.909          | 0 °   | 0.806           | -193.0°          | 0.826           | $-24.08^{\circ}$ |

| 7       | 0.212          | 0 °   | 0.381           | $-231.6^{\circ}$ | 0.519           | -100.9°          |

| 8       | 0.419          | 0°    | 0.343           | $-270.2^{\circ}$ | 0.285           | $-177.7^{\circ}$ |

Figure 12 – Normalized electric field for the code implemented in MATLAB and HFSS solution for  $\phi = 90^{\circ}$ , in dB.

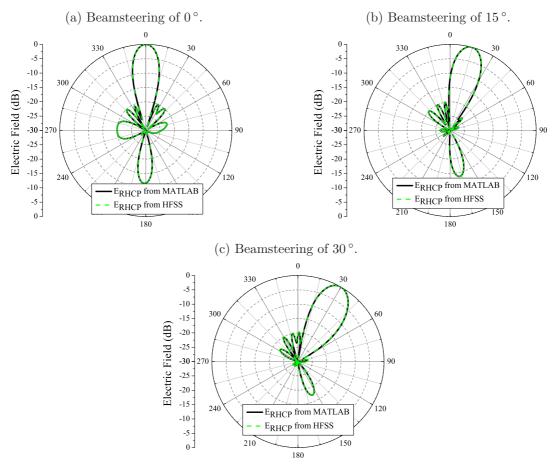

For practical implementation, an analysis including the effects of discretizing the magnitudes of the receiving signals has been performed. The analysis assumes the use of VGAs of the type DVGA1-24PP+. By considering that this device allows 64 levels of discretization and that the maximum gain is 31.5 dB, the gain step is  $\frac{31.5}{64} = 0.5$  dB (the minimum gain is 0.5 dB). The same three cases have been considered for optimization with PSO. However, for this analysis, PSO has been set up to consider only the 64 discretized magnitude levels allowed by the 6-bit digitally controlled VGA. The ideal and discrete magnitudes of the currents for the three synthesized radiation patterns are presented in Table 5. Fig. 13 shows the normalized electric fields obtained for the  $\phi = 90$ ° plane, where the continuous lines stand for PSO without considering discretization of the currents and the dotted lines represent the patterns obtained considering the performance of the VGA (MAGALHÃES et al., 2015). It can be observed that there was good suppression of the side lobes, but the SLL requirement could not be completely fulfilled in all the three analyzed cases.

Figure 13 – Normalized electric field for discrete and ideal control of the current magnitudes for  $\phi = 90^{\circ}$ , in dB.

Table 5 – Ideal and discrete current magnitudes for the cases of steering.

| Element | Steering of 0° |          | Steering of $15^{\circ}$ |          | Steering of 30° |          |

|---------|----------------|----------|--------------------------|----------|-----------------|----------|

| Element | Ideal          | Discrete | Ideal                    | Discrete | Ideal           | Discrete |

| 1       | 0.7935         | 0.7943   | 0.4620                   | 0.4732   | 0.1776          | 0.1778   |

| 2       | 0.5067         | 0.5012   | 0.3635                   | 0.3548   | 0.2113          | 0.2113   |

| 3       | 0.8620         | 0.8414   | 0.8424                   | 0.8414   | 0.7733          | 0.7499   |

| 4       | 1.0000         | 1.0000   | 1.0000                   | 1.0000   | 1.0000          | 1.0000   |

| 5       | 0.9656         | 0.9441   | 0.9360                   | 0.9441   | 0.7712          | 0.7499   |

| 6       | 0.9086         | 0.8913   | 0.8058                   | 0.7943   | 0.8264          | 0.8414   |

| 7       | 0.2122         | 0.2113   | 0.3809                   | 0.3758   | 0.5190          | 0.5309   |

| 8       | 0.4198         | 0.4217   | 0.3425                   | 0.3350   | 0.2852          | 0.2818   |

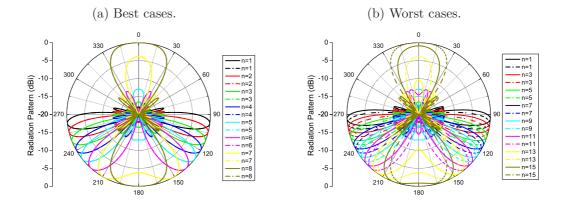

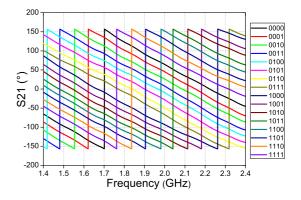

Due to the need of precision at the main lobe steering, it is interesting to perform an analysis about the impact of the phase shifter resolution at the final radiation pattern of the antenna array. Since the chosen phase shifter has 4-bit of control, there are  $2^4 = 16$  possible phase-shift values, in steps of  $\frac{360}{16} = 22.5$ °. In order to analyze the best and worst

cases, some tests were carried out. The best cases are achieved when the phase shift  $\beta$  is multiple of 22.5°, or  $\beta = n * 22.5$ ° for  $n = 0, 1, 2, 3, \dots$  Considering an antenna array with 8 isotropic elements, distance  $d = 0.5\lambda$  between the antennas and phase shift of  $\beta = 22.5$ °, it is known that the main beam will be pointed to

$$\beta = -2\pi d\cos\theta \longrightarrow \theta = \cos^{-1}(-\frac{\beta}{2\pi d}) = 97.18^{\circ}$$

(2.1)

Therefore, the difference between the ideal and the discretized cases for the best case is

$$\Delta \theta = \theta_{ideal} - \theta_{step} = 97.18^{\circ} - 97.18^{\circ} = 0^{\circ}$$

(2.2)

The worst cases occur when the phase shift  $\beta$  is an odd multiple of  $\frac{22.5}{2}$ , or  $\beta = n*11.25$ ° for n=1,3,5,... In this case, by assuming  $\beta = 11.25$ °, it comes out that

$$\beta = -2\pi d\cos\theta \longrightarrow \theta = \cos^{-1}(-\frac{\beta}{2\pi d}) = 93.58^{\circ}$$

(2.3)

The difference between the ideal and the discretized cases is

$$\Delta \theta = \theta_{ideal} - \theta_{step} = 93.58^{\circ} - 90^{\circ} = 3.58^{\circ} \tag{2.4}$$

As it can be observed at the worst case, the desired steering difference for the supplied step of the phase shifter is of  $3.58^{\circ}$  error in pointing the main beam close to the boresight ( $\theta = 90^{\circ}$ ), where the beam presents minimum beamwidth. Fig. 14 shows the normalized radiation pattern in dBi for the ideal and discretized cases for different steering directions, where the straight lines are pattern with the ideal values and the dotted lines are the ones for discretized phases.

Figure 14 – Normalized radiation pattern for ideal and discrete control, in dBi.

#### 2.3.2 Failure of one or more elements

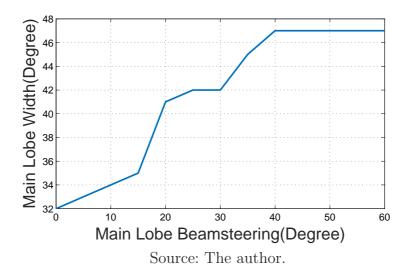

This parametric study was based on the antenna array behaviour using MATLAB software. The phase behaviour of the Rx-circuitry, the truncation phase and power amplitude of the Tx-circuit were included in the analysis performed by the heuristic PSO. The analysis is divided in two parts: the first presents results for a fully functional array, where all the elements are working properly and the second one was performed to consider the case where one element is off, so that the optimization methods try to adjust the amplitude of the excitation coefficients so as to compensate element failure. For comparison, the array patterns using amplitude tapering with the standard Dolph-Chebyshev weights were included (ENGROFF et al., 2016). The main lobe width is a function of the beamsteering as can be seen in Fig. 15. This relation is obtained from the average width of the main lobe through the supplied currents defined from Dolph-Chebyshev. A low penalty region of 1° was defined farther the limit set for the main lobe in the mask, which is necessary to model the main lobe shape in this region (ENGROFF et al., 2016).

The optimization algorithm goal is to maximize the directivity for the main lobe steering angle. The maximum directivity used as a reference was 13 dBi. Thus, the cost function meets the following equation

$$F_{cost} = DD \cdot P_1 + LPA \cdot P_2 + HPA \cdot P_3 \tag{2.5}$$

Where DD is the difference between the obtained and desired directivity, LPA is the area above the mask in the low penalty region, HPA is the area above the mask in the high penalty region,  $P_1$ ,  $P_2$  and  $P_3$  are the weights for each parameter. The weights  $P_1 = 0.2$ ,  $P_2 = 0.5$  and  $P_3 = 1$  were obtained empirically by seeking the best cost results.

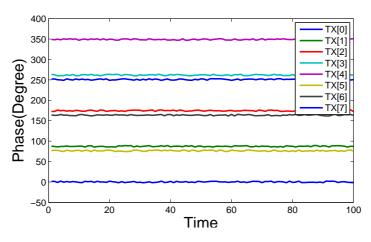

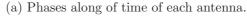

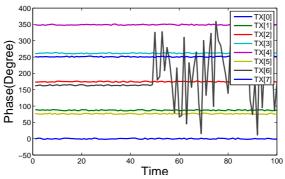

#### 2.3.2.1 Fully functional array

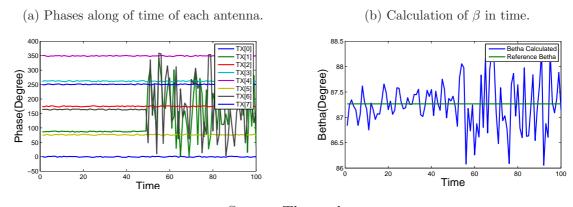

To simulate a fully functional array, a phase noise of  $\pm 4^{\circ}$  was introduced with random variation for the case of steering the main beam to  $-30^{\circ}$ . Fig. 16a shows the simulated phases for each element of the Rx-circuit. The calculation of the mean difference of the phases ( $\beta$ ) for the Tx-circuit is shown in Fig. 16b, with the reference value indicating the actual  $\beta$ , that is calculated by the following equations

$$\beta = \frac{\sum\limits_{i=1}^{8} \beta_i}{8} \tag{2.6}$$

$$\beta_i = Phase_i - Phase_{i+1} \tag{2.7}$$

Figure 16 – Analysis for beamsteering to  $-30^{\circ}$  for a fully functional array.

(a) Phases along of time of each antenna.

(b) Calculation of  $\beta$  along of time.

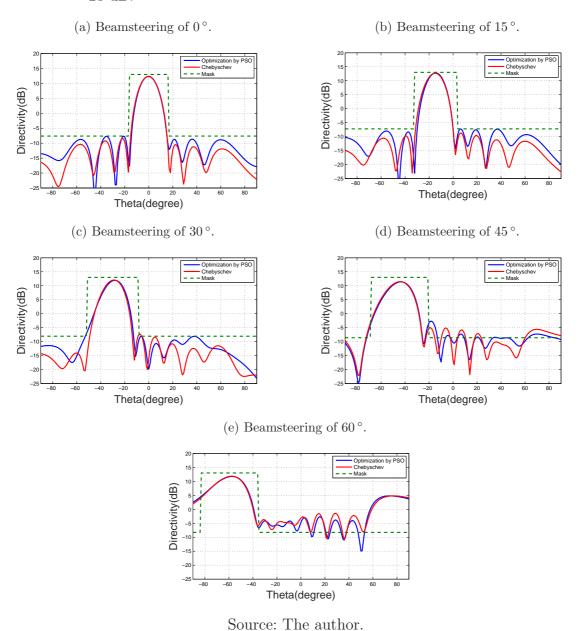

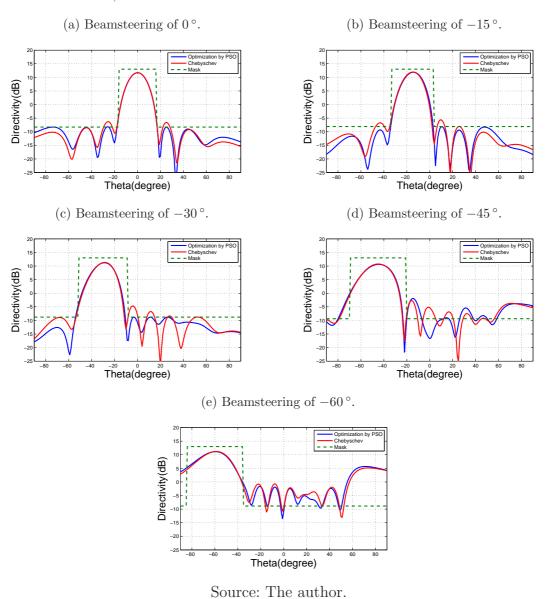

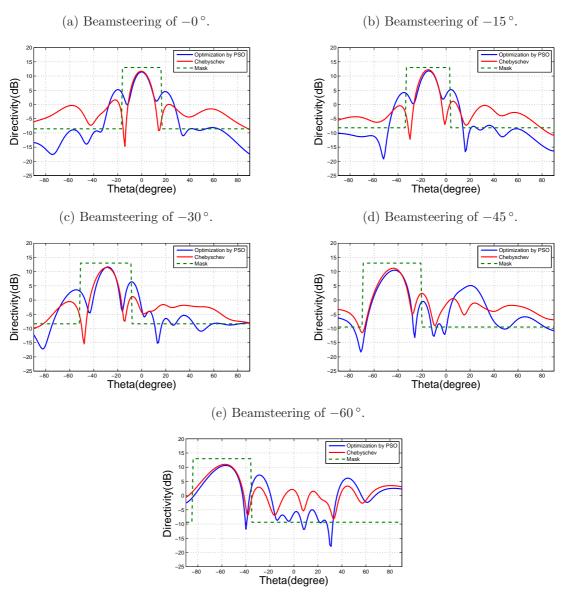

The optimized patterns are shown in Fig. 17 for different beamsteering direction and SLL = -20 dB. For the first two cases, the algorithm could optimize the pattern and fulfill the specifications. By steering the main beam to  $-45^{\circ}$  and  $-60^{\circ}$ , one can see that the constraints regarding the side lobe levels could not be fully fulfilled.

Figure 17 – Optimized patterns for different beamsteering angles considering SLL = -20 dB.

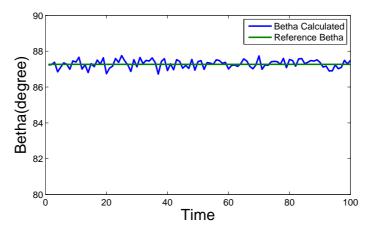

#### 2.3.2.2 Array with faulty element in the receiver

In order to test the ability of determining the  $\beta$  values with tolerance to failure in the Tx-circuit, tests with loss of one and two elements in the Rx-circuit were performed. The main lobe is steered to  $-30^{\circ}$ . The obtained results for the phases of each element of the Rx-circuit are shown in Fig. 18a. The value of the calculated  $\beta$  for the Rx-circuit is

shown in Fig. 18b. As it can be seen, the variation of  $\beta$  is estimated between  $\pm 4^{\circ}$ . For the failure of two elements, the phases of the elements are shown in Fig. 19a. The calculated  $\beta$  for the Rx-circuit is shown in Fig. 19b. The variation of  $\beta$  is in the range of  $\pm 4^{\circ}$ . This demonstrates that the average calculation for determining the  $\beta$  is robust to loss of up to two elements.

Figure 18 – Analysis for beamsteering to  $-30^{\circ}$  with loss of one element of Rx-circuit.

(b) Calculation of  $\beta$  in time.

Source: The author.

Figure 19 – Analysis for beamsteering to  $-30^{\circ}$  with loss of two elements of Rx-circuit.

#### 2.3.2.3 Array with faulty element in the transmitter

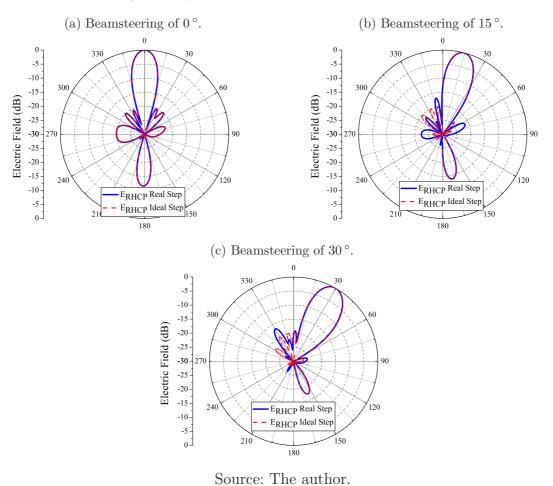

In order to test the beamforming capabilities under the case of one faulty element in the array, two situations were considered: failure of element 1 and element 4. In the same steering cases considered in the previous analysis, the optimized patterns are shown in Figs. 20 and 21. To visualize the impact of element failure, the pattern obtained with Dolph-Chebyshev distribution is plotted as a reference (ENGROFF et al., 2016). The graphics show that the loss of element 1 is not as critical as it is for the case of losing element 4, since better results are obtained for the first case in comparison to the latter. This can be expected, since failure of element 1 results in a still uniform linear array with reduced size. Finally, for beam steering to  $-45^{\circ}$ ,  $-60^{\circ}$  and failure of element 4, the PSO fails to achieve the desired specifications.

Figure 20 – Optimized patterns for different beamsteering angles considering SLL = -20 dB, and failure of element 1.

Figure 21 – Optimized patterns for different beamsteering angles considering SLL = -20 dB, and failure of element 4.

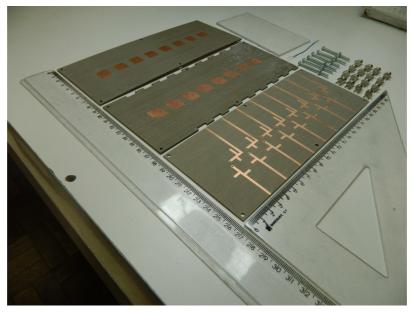

### 2.4 Antenna Array Prototype and Measured Results

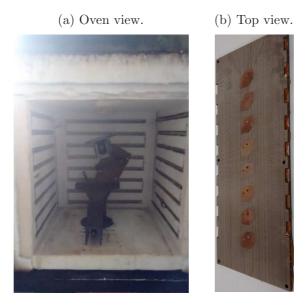

Based on the antenna array design specifications stated previously, the simulated topology was prototyped. All the specifications were followed in order to obtain the best agreement between simulation and measurement as possible. As well known, antennas operating at high frequencies are not easily prototyped, because of the high sensitivity to fabrication tolerances. The first step consisted on prototyping the three layers of patches and transmission lines as shown in Fig. 22.

Figure 22 – Prototyped antenna array layers.

After that, the transmission line layer (bottom layer) was glued to the bottom patches that operate at 5.8 GHz (medium layer) with the prepreg (FR27). For good alignment between layers, four screws were used at the corners during the gluing process. The two layers were placed in the oven at conditions of pressure and temperature recommended by the glue manufacturer, as it can be seen in Fig. 23. The next step consisted on soldering the SMA connectors and the vias between the transmission lines to the patches working at 5.8 GHz, as shown in Fig. 24.

Figure 23 – Prototype prior to and after glueing.

Figure 24 – Soldered vias for lower frequency patches.

(a) Top view.

(b) Bottom view.

Source: The author.

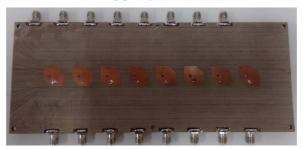

Finally, the top layer was attached to the two glued layers. An important issue is to keep the air gap exactly the same as for the simulated structure. In this case, acrylic blocks were used during the soldering process. The vias were soldered first, since they also help to keep the correct air gap. The final prototype structure is shown in Fig. 25.

Figure 25 – Prototyped final structure for the retrodirective antenna array.

(a) Top view.

(b) Bottom view.

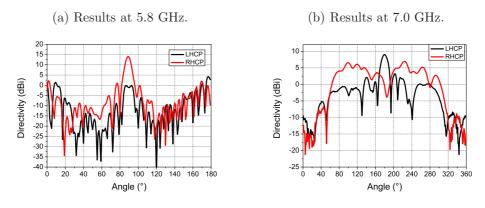

The measured S-parameters at both bands were performed and small deviations between the ports were verified in both operating frequencies, as it can be seen in Fig. 26. A slight frequency shift can be observed in both bands, but the required bandwidth was still achieved. The main reason for that is the inaccuracy of the air layer thickness of the prototype, especially for dual-frequency and dual-polarization antennas. Therefore, taking into account such difficulties, the results are considered to be acceptable.

Figure 26 – Measured reflection coefficient for both frequencies.

Source: The author.

The radiation patterns were measured at the DLR anechoic chamber and are shown in Fig. 27. The radiation pattern measurements were carried out for each element separately, while the other elements were terminated with matched loads. Then, the resultant radiation pattern was calculated from the vector sum of the measured patterns. One can see that the cross-polarization decoupling is degraded compared to the simulated results. This is also a consequence of the tolerance in the fabircation process, as alignment between the dielectric layers and the air gap thickness. This conclusion were drawn based on the parametric analysis for the dual-band and dual-polarized antenna behaviour described in (PEREIRA, 2015) for the single antenna.

Figure 27 – Measured radiation pattern for both frequencies.

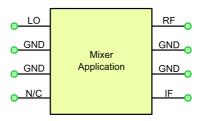

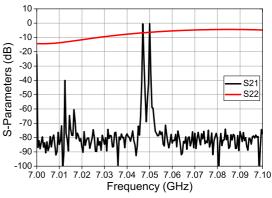

# 3 RF Front-end Circuits

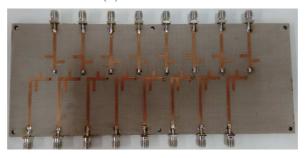

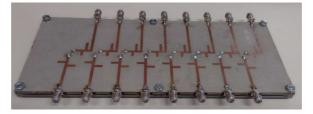

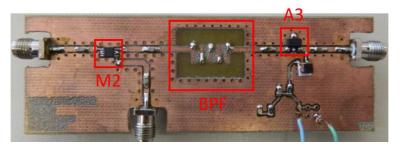

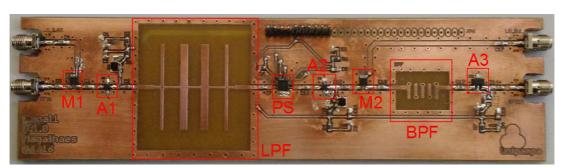

The second goal of this work is the design of Tx-circuitry. This work has been partially done in collaboration with the German Aerospace Center (DLR). In the following sections, the design and measurements of the RF components are presented. The goal is to develop the Tx-circuitry with low cost and by using off-the-shelf components.

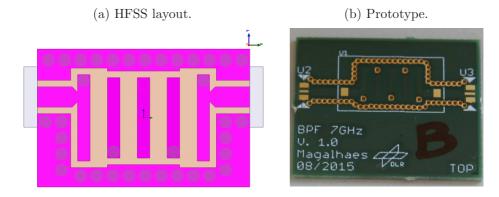

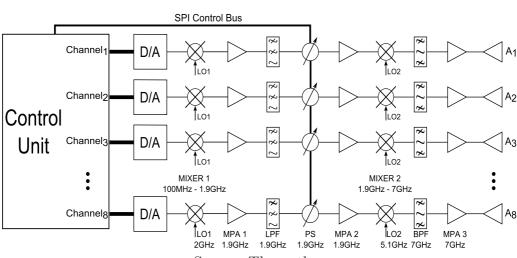

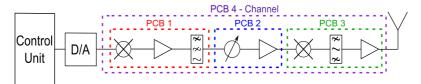

The initial architecture of the Tx-circuitry is shown in Fig. 28. It is composed of two stages of amplification (MPA1 and MPA2) to compensate the insertion loss of the passive components, and to amplify the signal that is generated by the FPGA. Also, two stages of mixers (MIXER1 and MIXER2) are necessary due to the low operation frequency of the digital-to-analog converters (D/As) (100 MHz) compared to the RF frequency required for the transmission signal. Then, the variable gain amplifiers (VGA) and the phase shifters (PS) are used to control the amplitude and phase to be provided to each antenna to perform the beamforming. Some stages of filters (LPF and BPF) to cutoff the undesired frequency range and directional couplers (DC) for calibration and verification of the signal were desgined.

SPI Control Bus Channel<sup>2</sup> D/A Channel D/A Control Channel D/A Unit MIXER 1 MIXER 2 Channela D/A LPF BPF LO1 LO2 MPA 1 VGA DC MPA 2 100MHz 2GHz 1.9GHz 1.9GHz 1.9GHz 5.1GHz 7GHz 7GHz Source: The author.

Figure 28 – Initial architecture for the Tx-circuitry.

For the designed PCBs, some specifications to reach the best performance as possible were followed. The RF chokes must be positioned near of the RF lines in order to decrease the losses. For good impedance matching, the RF lines (coplanar waveguides - CPW) must be designed with width of 1.5 mm and gap of 0.5 mm. The lines were designed with bends of exactly 45  $^{\circ}$  of inclination in the corners to keep a good signal propagation. Connections to ground using via holes to reduce ground path inductance were used.

## 3.1 Design of the Individual Components

## 3.1.1 Medium power amplifier - first stage

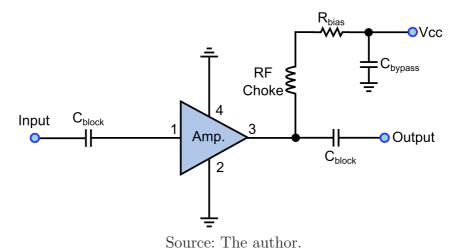

The first stage of medium power amplifier (MPA1) was designed in order to reach the required power level, since the mixers and filtering stages have significant insertion loss. The signal is provided by the digital-to-analog at a maximum frequency of 100 MHz. In this case, the component ERA-1SM+ from Mini-Circuits was chosen. This component is a broadband amplifier that works from DC to 8 GHz, hence being flexible to use in any frequency range of the transmitting channel. Fig. 29 shows the recommended application circuit for ERA-1SM+.

Figure 29 – Electric circuit for the medium power amplifier ERA-1SM+.

The external components have the following functions: for the  $RF_{in}$ , the use of an external DC-blocking capacitor is required. Regarding the  $RF_{out}$ , a blocking capacitor and an RF choke were necessary for the DC feeding. According to the datasheet, the DC feeding can be chosen in a flexible way. In this case, a DC supply of 12 V was used. A resistor for optimum biasing and a capacitor for bypass were used. This capacitor is used to filter out the AC signals. The provided S-parameters specifications from the datasheet are  $S_{11} = -30.0$  dB,  $S_{12} = -17.0$  dB,  $S_{21} = 12.3$  dB and  $S_{22} = -26$  dB.

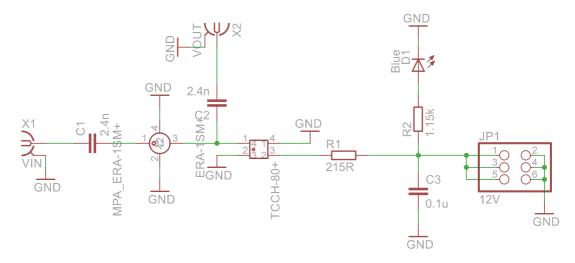

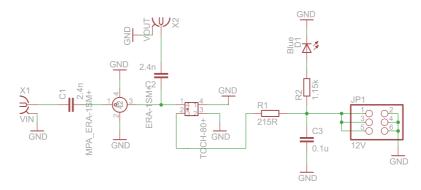

#### 3.1.1.1 First prototype

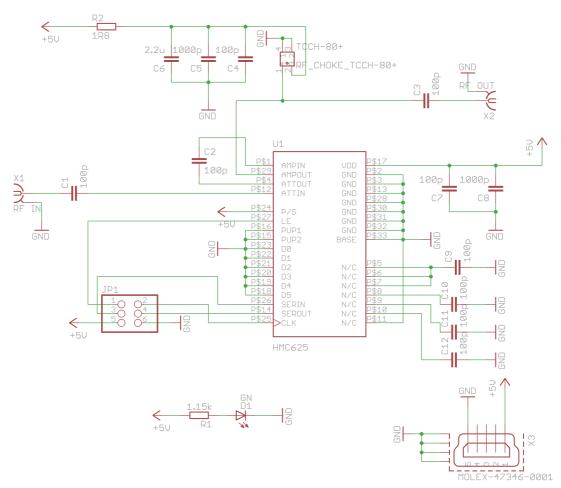

The second step consists on the electrical schematic design. Following the defined specifications, the schematic was designed and is shown in Fig. 30. As it can be observed, for the MPA1 circuit, the following components were used: pinheads for DC feeding, SMA connectors for the RF input and output, capacitors of 100 pF for DC blocking and 0.1  $\mu$ F for bypass, resistor of 215  $\Omega$  and RF choke TCCH-80+ for biasing.

Figure 30 – Designed schematic for the medium power amplifier ERA-1SM+, first prototype.

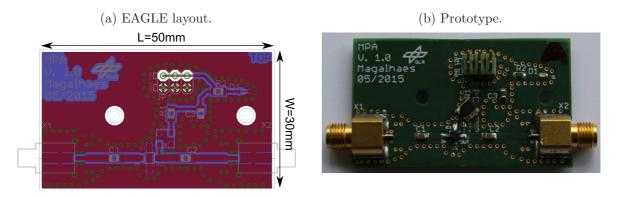

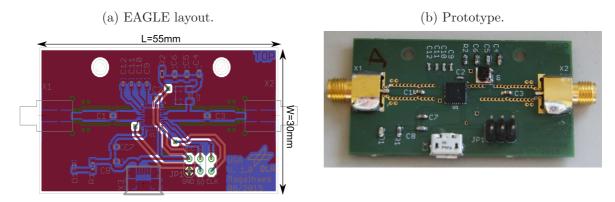

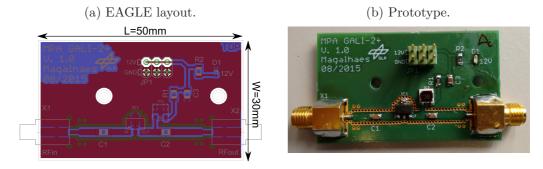

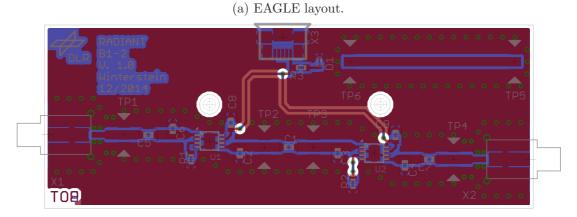

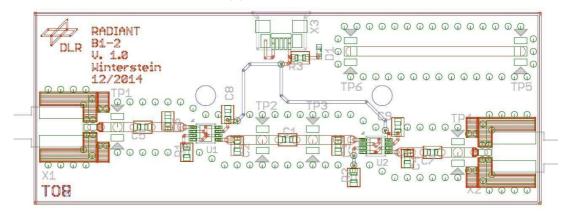

Once the schematic has been created, the layout has been generated. The components have been organized in order to save space as much as possible, respecting the following rules to keep good performance: adequate spacing between adjacent lines, correct width of the lines and the insertion of vias. Fig. 31 shows the final layout designed on EAGLE and the prototype.

Figure 31 – Layout designed for the medium power amplifier ERA-1SM+, first prototype.

Source: The author.

#### 3.1.1.2 Second prototype

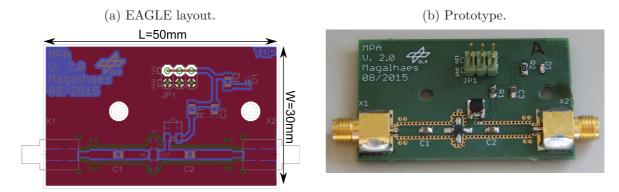

In the first stage of medium power amplifier, a new design was necessary to improve the performance and correct the RF choke soldering, which was provided wrongly in the datasheet of the component. The final schematic is shown in Fig. 32. Fig. 33 shows the final layout designed on EAGLE and the new prototype.

Figure 32 – Schematic designed for the medium power amplifier ERA-1SM+, second prototype.

Figure 33 – Layout designed for the MPA ERA-1SM+, second prototype.

Source: The author.

#### 3.1.1.3 Measurement and simulation results

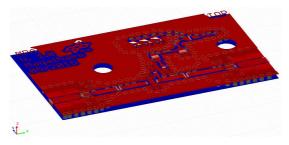

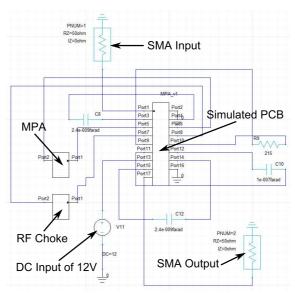

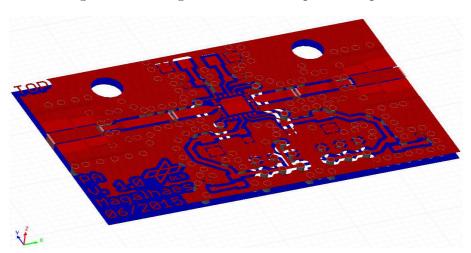

For the first production of medium power amplifier, the PCB simulation was performed. The details about PCB simulation are described in Chapter 4, where a step-by-step procedure on how to simulate PCBs using Ansys software is given. Fig. 34 shows the simulated PCB in the HFSS/Designer software.

Figure 34 – Electromagnetic model of the PCB for the medium power amplifier ERA-1SM+, first prototype.

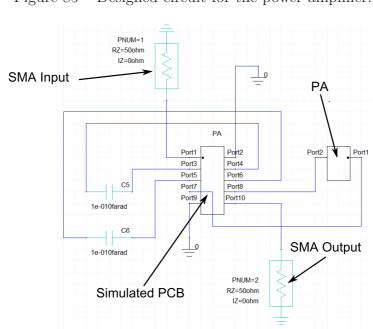

Then, with the simulated PCB and the definition as an N-Port model in the circuit design, the components ERA-1SM+, resistors and capacitors may be connected to perform the final simulation. The simulated circuit is shown in Fig. 35.

Figure 35 – Schematic circuit for the MPA ERA-1SM+, first prototype.

Source: The author.

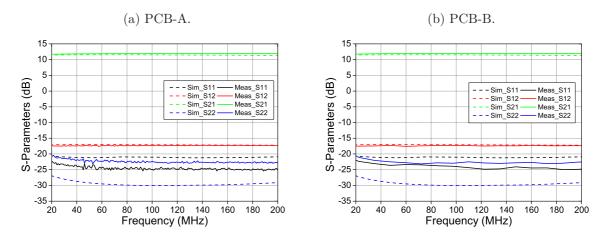

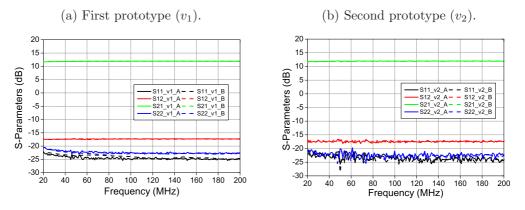

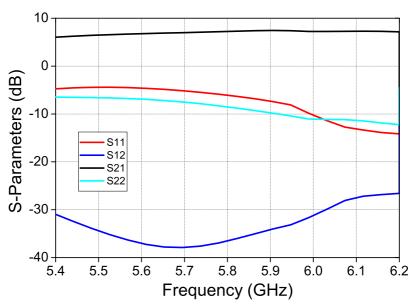

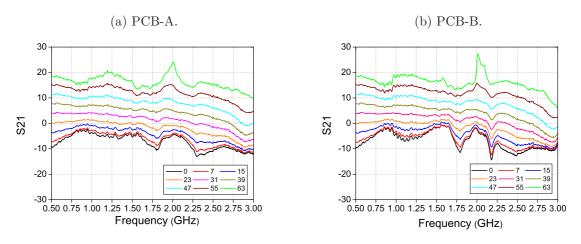

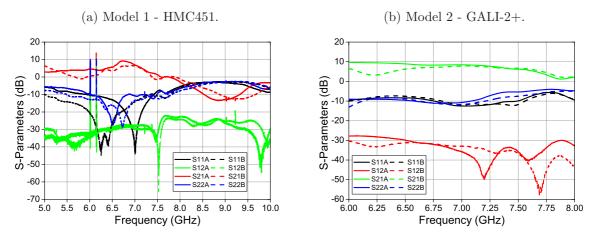

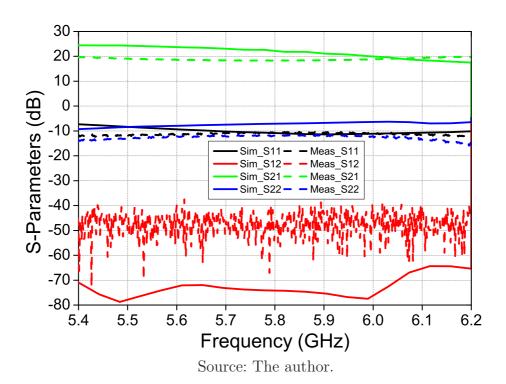

In order to compare the simulation and measured results, the S-parameters were traced in the same graph. As it can be observed in Fig. 36, the simulated and measured results are similar, hence proving that the simulation is a good option to analyze the RF behaviour before the assembly. To check the reproducibility, more than one PCB were soldered and measured. Therefore, the letters A and B stand for the different PCBs assembled.

Figure 36 – Simulated and measured results for the assembled PCBs of medium power amplifier ERA-1SM+, first prototype.

Fig. 37 shows the measured S-parameters for both prototype versions. As it can be observed, good results based on the component specifications in terms of reflection and transmission coefficients were obtained. The gain in the operation frequency of 100 MHz was 12.3 dB, which is in agreement with the performance given by the manufacturer.

Figure 37 – Measured results for both prototypes of medium power amplifier ERA-1SM+.

Source: The author.

## 3.1.2 Mixer - first stage

The first stage of frequency translation (MIXER1) has the function to convert the signal from 100 MHz to 1.9 GHz. This is needed due to the operating band of the phase shifter. To design the mixer electrical circuit, some specifications must be defined. The local oscilator (LO) frequency is chosen from the required intermediate frequency (IF) and RF signals, generating an output at 1.9 GHz. For this purpose, the LO frequency chosen was 2.0 GHz, and the two RF output signals are given by:

$$RF_{out1} = LO - RF_{in} = 1.9 \text{ GHz}$$

$$(3.1)$$

$$RF_{out2} = LO + RF_{in} = 2.1 \text{ GHz}$$

(3.2)

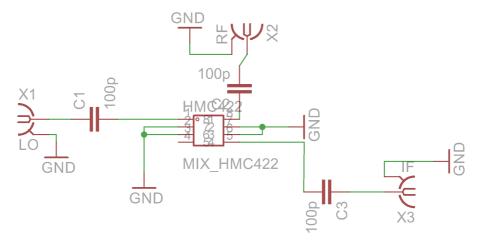

For active circuits (DC feeding system), the use of external DC blocking capacitor is necessary at the  $IF_{in}$  and  $RF_{out}$  signals. For passive circuits (without DC feeding), this is not necessary, since there is no DC signal through the circuit. In the active case, the DC voltage for the LO amplifier was 3.3 V. Also, one external RF bypass capacitor is required as for the MPA. For the MIXER1 stage, two prototypes were desgined. In the first prototype, the active mixer device HMC422 was used. The manufacturer specifications are conversion loss of 8 dB and LO power of 0 dBm. For the second prototype, the passive mixer device HMC316 was tested. The manufacturer specifications are conversion loss of 8 dB and LO power of 15 dBm.

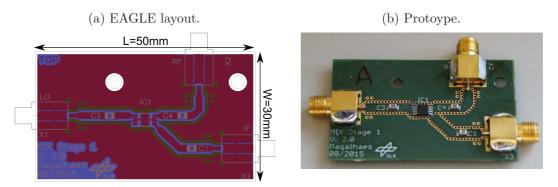

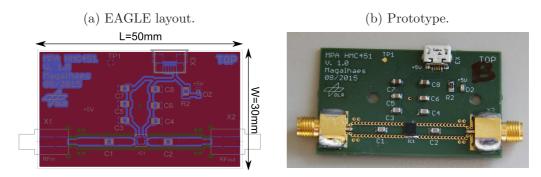

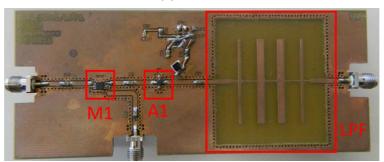

## 3.1.2.1 First prototype

Fig. 38 shows the connections of the active mixer. The schematic is shown in Fig. 39. For proper operation, components as mini USB for DC feeding, SMD capacitors of 100 pF for DC blocking, capacitor of  $0.1\mu F$  for bypass and SMA connectors of 50  $\Omega$  for LO, IF and RF were used. Fig. 40 shows the final layout designed and the prototype produced for the MIXER1 stage.

Figure 38 – Device connections for the MIXER1 stage, first prototype.

Source: The author.

Figure 39 – Schematic designed for the MIXER1 stage, first prototype.

Source: The author.

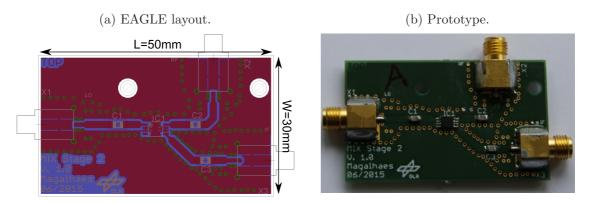

Figure 40 – Layout designed for the MIXER1 stage, first prototype.

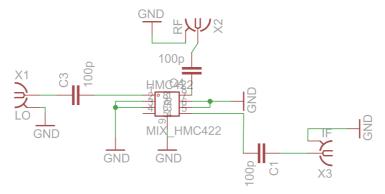

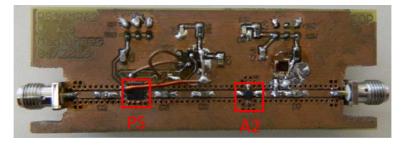

### 3.1.2.2 Second prototype

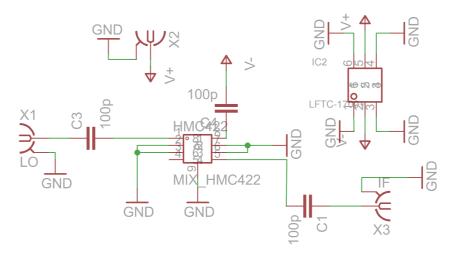

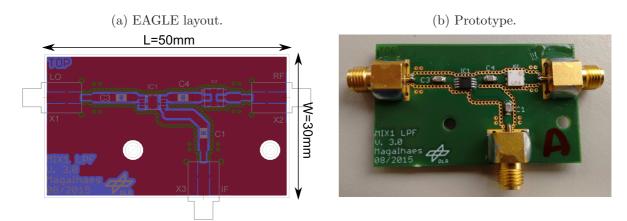

In the second prototype of the same MIXER1 stage, some adjustments in the PCB layout were required due the different device characteristics. Fig. 41 shows the device connections of the passive mixer. The schematic is shown in Fig. 42. As it can be observed, by comparing both productions, this component does not need a DC feeding nor bypass or blocking capacitors due the presence of only AC signal. Fig. 43 shows the final layout designed and the prototype.

Figure 41 – Device connections for the MIXER1 stage, second prototype.

Source: The author.

Figure 42 – Schematic designed for the MIXER1 stage, second prototype.

Source: The author.

Figure 43 – Layout designed for the MIXER1 stage, second prototype.

Another test was done with the mixer with an integrated monolitic filter. The used low-pass filter is the LFTC-1700, which was used to cutoff the image frequency higher than 1.95 GHz. For this design, the passive mixer used for the second production was considered. The electrical schematic circuit was designed and is shown in Fig. 44. Fig. 45 shows the final layout designed and the prototype.

Figure 44 – Schematic designed for the MIXER1 stage with filtering, second prototype.

Source: The author.

Figure 45 – Layout designed for the MIXER1 stage with filtering, second prototype.

Source: The author.

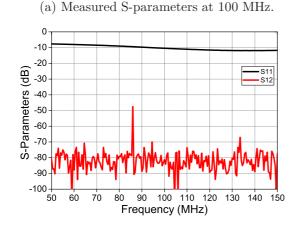

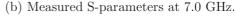

#### 3.1.2.3 Measurement results

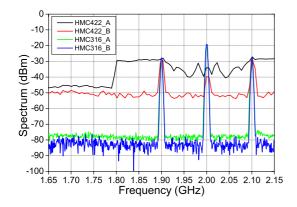

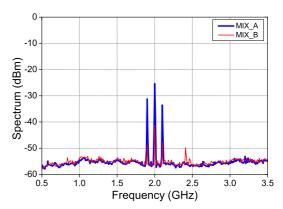

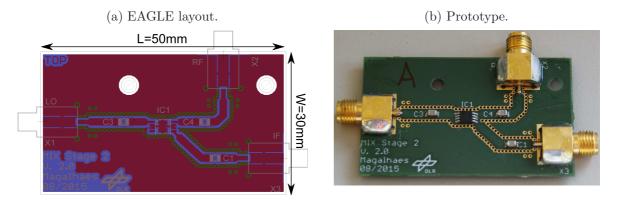

Since the manufacturers of the employed mixers do not provide the required S-parameters files (.s3p or touchstone format), it was not possible to simulate the PCB. Therefore, only the measurement results are shown in Fig. 46, where the cases with and without filtering stage are plotted.

Figure 46 – Measurement results for the MIXER1 stage.

(a) Without filtering stage, both prototypes.

(b) With filtering stage, second prototype.

Source: The author.

As it can be observed in Fig. 46, the results are presented in terms of spectrum as a function of the frequency. The RF output signal is a combination of the LO and IF as commented previously. Therefore, there are two generated signals by the combination of the LO = 2 GHz and the IF = 100 MHz: the sum resulting at 2.1 GHz and the subtraction resulting at 1.9 GHz, which is the desired frequency for the RF output. The active mixer did not present good results based on the component specifications in terms of spectrum. Although the needed LO power is lower than the RF signal level, the disadvantage of such circuit is the sensibility. During the tests, several mixers burned and, therefore, it was not possible to check the reproducibility. For two prototypes of this PCB (A and B), just one worked properly.

Both passive mixers worked well based on the component specifications as shown in Fig. 46. Due to the stability of passive devices, this mixer was chosen to the implementation of the Tx-circuitry. Also, the expected performance was reached in terms of conversion loss (around 8 dB). Prototypes A and B for the passive mixer resulted in very similar results; hence reproducibility has been verified.

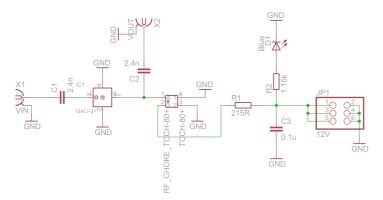

## 3.1.3 Low-pass filter operating at 1.9 GHz

In many projects, the use of filters are of extreme importance, since just a desired frequency range can be processed, decreasing the performance deterioration generated by interferences. The use of filters allows keeping the frequency range and cutoff the undesired signal. However, is not easy to find a filter that operates at 5.8 GHz and 7.0 GHz with small size and low cost. A design of Low-Pass Filter (LPF) and Band-Pass Filter (BPF) using coplanar waveguide (CPW) technology were defined. For frequencies of 7.0 GHz and 1.9 GHz, the FR4 substrate was chosen. This substrate is commonly used for circuit applications, since it is cheap and easily available in the market. Also, this allows integra-

ting the filters directly into the Tx-circuitry. One technique to design filters in CPW is to convert an electrical circuit into a distributed equivalent microstrip. As known from the literature, low-pass filters can be formed by the association of capacitors and inductors (SAYRE, 2001).

The first step consists in defining the design specifications for the LPF: operation frequency of f=1.9 GHz, input and output impedance of  $R_0=50~\Omega$ , inductors impedance of  $Z_1=120~\Omega$ , and capacitors impedance of  $Z_2=20~\Omega$ . The FR4 material used at DLR has the dielectric constant of  $\varepsilon_r=4.4$ , loss tangent of  $\delta=0.02$  and thickness of 1.0 mm. The FR4 material used at UNIPAMPA has different thickness of 1.6 mm. For this reason, new optimizations of the model were necessary. This choice was made considering that this filter will be integrated into the Tx-circuitry to cutoff the undesired frequency range generated by the MIXER1 stage.

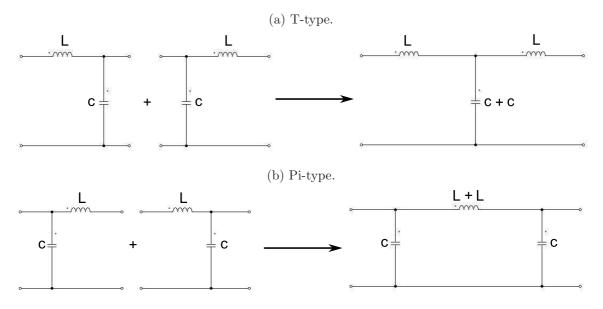

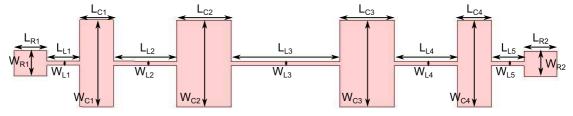

For the LPF, a ninth order topology was chosen. As known, when the order is increased, the attenuation also increases. The inductances and capacitances necessary to design the filter will be defined in the next sections. For such kind of filter, two configurations of series inductors and shunt capacitors were used: the LPF T-type and Pi-Type. Fig. 47 shows the different topologies.

Figure 47 – Different techniques to merge LC circuits in LPF designs.

Source: The author.

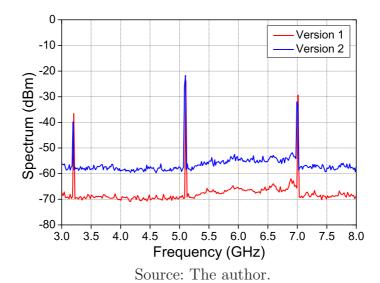

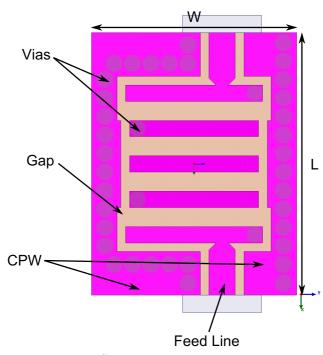

The LPF was designed considering the coplanar waveguide technology, as shown in Fig. 48. As it can be seen, such model is composed of the feed line composed coplanar waveguide with gap of 0.5 mm between the feed line and ground. The vias act as a shield for the RF signal around the RF lines, thereby, decreasing the losses.

Vias Gap CPW Feed Line

Figure 48 – Adopted structure for the LPF design.

#### 3.1.3.1 Calculation of the initial parameters

To define the cutoff frequency  $(f_c)$ , it is necessary to multiply f by a correction factor (ADJ) to avoid that  $f_c$  decreases with the increase of the filter order. This is referred as the cascade effect, when there are two or more combinations of half-sections (SAYRE, 2001). Table 6 shows the ADJ factor as a function of the number of sections.

Table 6 – Correction factor for different number of sections.

| Number of Sections        | ADJ    |

|---------------------------|--------|

| (1/2  Section = 2  Poles) | Factor |

| 0.5                       | 1.00   |

| 1.0                       | 1.05   |

| 1.5                       | 1.10   |

| 2.0                       | 1.15   |

| 2.5                       | 1.20   |

| 3.0                       | 1.25   |

Source: The author.

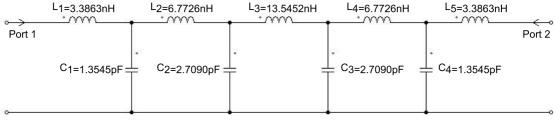

If one pole is equivalent to 1/4 sections, then the number of sections for a ninth order filter is 9/4 = 2.25 and the ADJ factor will be 1.175. In order to guarantee that the center frequency of the IF signal is located in the pass-band of the filter, a margin of BW = 100 MHz has been considered. Therefore, the cutoff frequency will be

$$f_c = (f + BW)ADJ = (1.9 \text{ GHz} + 100 \text{ MHz})1.175 = 2.35 \text{ GHz}$$

(3.3)

After calculating the cutoff frequency, it is possible to define the primary inductances and capacitances using the following equations

$$L = \frac{R_0}{2\pi f_c} = 3.3863 \text{ nH} \tag{3.4}$$

$$C = \frac{1}{2\pi f_c R_0} = 1.3545 \text{ pF}$$

(3.5)

#### 3.1.3.2 Definition of the electrical circuit

Using the logic of half-sections applied to a ninth order LPF, the resulting electrical circuit considering the inductances and capacitances calculated above is shown in Fig. 49.

Figure 49 – Defined electrical circuit for the LPF operating at 1.9 GHz.

Source: The author.

#### 3.1.3.3 Convertion of the components to equivalent microstrip lines

After the LPF electrical circuit has been designed, it is necessary to convert the lumped model to an equivalent distributed structure. Some calculations can be performed to estimate the width and the length of each microstrip line. Fig. 50 shows a microstrip structure using equivalent microstrip sections.

Figure 50 – Microstrip lines equivalent to lumped components.

Source: The author.

The lengths and widths can be calculated using the proper equations to calculate the electrical lengths, and determinating the width through the required impedance; or using an estimation software as Txline (free software available online) to estimate both parameters considering the defined specifications. If the first method is chosen, Eq. (3.6) for capacitors and (3.7) for inductors can be used.

$$L_C = \lambda(tan^{-1}(6.28f_c20C)) \tag{3.6}$$

$$L_L = \lambda (\sin^{-1}(\frac{6.28f_cL}{120})) \tag{3.7}$$

$$\beta l_C = \frac{C'Z_0}{R_0} \tag{3.8}$$

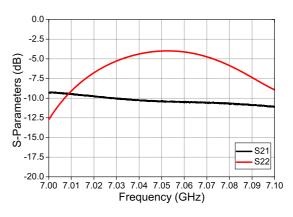

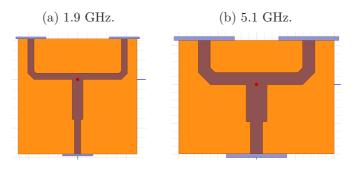

$$\beta l_L = \frac{L'R_0}{Z_0} \tag{3.9}$$